Chipverpackung

IC -PCB & Verpackung- Wenn Sie über die Zukunft der tragbaren Technologie sprechen, Der zukünftige Verlauf der tragbaren technologischen Innovation ist klar. Es ist laut und klar, dass der Erfolg, tragbare Elektronik muss klein sein und dennoch funktioniert. Dieser Artikel konzentriert sich auf die Anforderungen an Wafer – Level -Chip – Levelverpackung in SRAM .

Fußabdruck reduzieren, und damit der gesamte Board -Raum, Mikrocontroller migrieren zu kleineren Prozessknoten bei jeder anderen Generation. Gleichzeitig, Sie entwickeln sich, um komplexere und leistungsfähigere Operationen auszuführen. Wenn Operationen komplexer werden, Es ist dringend erforderlich, das Caching zu erhöhen. Bedauerlicherweise, Mit jedem neuen Prozessknoten, Hinzufügen eines eingebetteten Cache (eingebettete SRAM) wird aus mehreren Gründen schwierig, einschließlich höherer Ser, niedrigere Ausbeute, und höherer Stromverbrauch. Kunden haben auch kundenspezifische SRAM -Anforderungen. Für die MCU -Hersteller müssen alle möglichen Cache -Größen ein Produktportfolio haben, das zu groß ist, um es zu verwalten. Dies hat dazu geführt.

Jedoch, Da ein externes SRAM eine große Menge PCB -Platine einnimmt, Die Verwendung externer SRAM steht vor der Herausforderung der Miniaturisierung. Aufgrund seiner Sechs-Transsistor-Architektur, Reduzierung der Größe des externen SRAM, indem das externe SRAM auf einen kleineren Prozessknoten portiert wird.

Dies bringt uns zur nächsten Alternative zu diesem uralten Problem: Reduzierung des Verhältnisses der Chipverpackung zur Chipgröße im externen SRAM. Typischerweise, verpackte SRAM -Chips sind um ein Vielfaches der Größe des nackten Chips (bis zu 10 mal). Eine häufige Lösung für dieses Problem besteht darin, eingekapselte SRAM -Chips überhaupt nicht zu verwenden. Es ist sinnvoll, einen SRAM -Chip zu nehmen (1/10 Größe) und packen Sie es dann mit einem MCU-Chip mit komplexen Multi-Chip-Verpackungen ein (MCP) oder 3D -Verpackungstechnologie (Auch als Verpackung auf SIP-Systemebene bekannt). Dieser Ansatz erfordert jedoch erhebliche Investitionen und ist für die größten Hersteller nur machbar. Aus Designperspektive, Dies reduziert auch die Flexibilität, da Komponenten in SIP nicht einfach ersetzt werden. Zum Beispiel, Wenn die neue Technologie SRAM verfügbar ist, Wir können den SRAM -Chip in SIP nicht einfach ersetzen. Ersetzen eines der nackten Chips im Paket, Der gesamte SIP muss neu authentifiziert werden. Die Requalifikation erfordert Reinvestition und mehr Zeit.

Gibt es also eine Möglichkeit, den Vorstandsraum zu sparen und gleichzeitig das SRAM von der MCU auszuschließen, ohne den MCP in Schwierigkeiten zu bringen? Zurück zum Größenverhältnis von Core zu Chip, Wir sehen Raum für eine erhebliche Verbesserung. Warum prüfen Sie nicht, ob es ein Paket gibt, das fest in die Form passt?? Mit anderen Worten, Wenn Sie nicht auspacken können, Bitte reduzieren Sie die Größenskala.

Derzeit ist der fortschrittlichste Ansatz, die Größe des Chippakets durch WLCSP zu reduzieren (Paket Level Level Level Level Level). WLCSP bezieht sich auf die Technologie, einzelne Einheiten aus einem Wafer in kleine Stücke zu schneiden und sie dann in einem Paket zusammenzustellen. Das Gerät ist im Wesentlichen ein nackter Chip mit einem erhöhten Punkt oder einem kugelförmigen Array -Muster, für das keine Verbindungslinien oder Zwischenschichtverbindungen erforderlich sind. Abhängig von den Spezifikationen, Der Bereich eines Chip-Level-Pakets ist bis 20% größer als der des Chips. Der Prozess hat nun ein innovatives Niveau erreicht, auf dem Produktionsanlagen CSP -Komponenten produzieren können, ohne den Chipbereich zu erhöhen (mit nur einem leichten Anstieg der Dicke, um die Beule/Kugel zu passen).

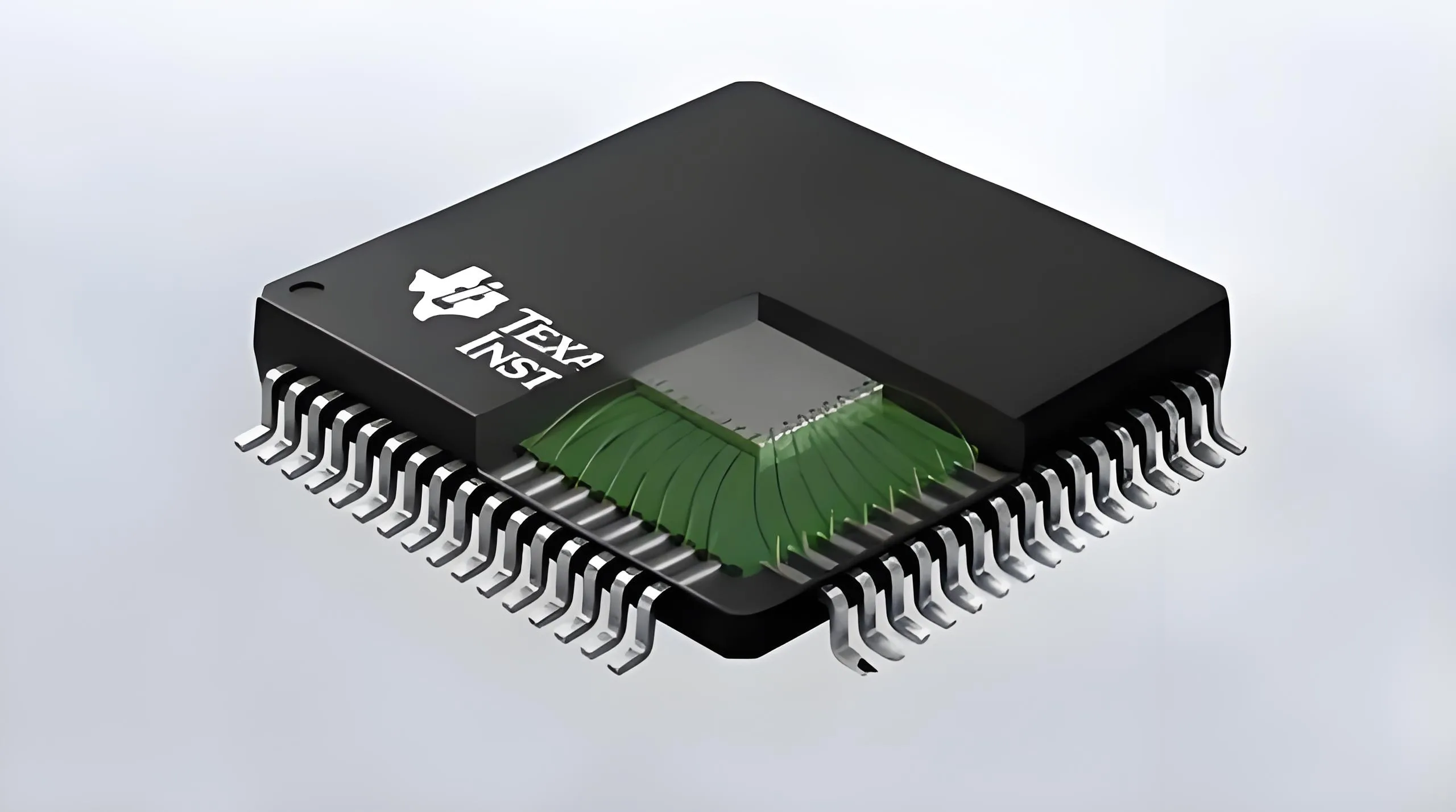

Zahlen. Wafer – An – Chipverpackung (Ulc) Bietet die fortschrittlichste Methode zur Reduzierung der Größe des verpackten Back – Chip. Das hier gezeigte WLCSP wurde von DECA -Technologien entwickelt und erhöht den Bereich der Chips, aus denen es besteht, nicht. (Kredit: Deca Technologies/ Cypress Semiconductor)

CSP hat einige Vorteile gegenüber unbeschichteter Film. CSP -Geräte sind einfacher zu testen, handhaben, montieren, und umschreiben. Sie haben auch verbesserte Eigenschaften der thermischen Leitfähigkeit. Wenn der Kern auf neuere Prozessknoten übertragen wird, Es ist möglich, den Kern zu reduzieren und gleichzeitig die CSP -Größe zu standardisieren. Dies stellt sicher, dass CSP -Komponenten durch eine neue Generation von CSP -Komponenten ersetzt werden können, ohne dass Komplikationen im Zusammenhang mit der Änderung der Form verbunden sind.

Offensichtlich, Diese Raumeinsparungen sind wichtig für die Nachfrage nach Wearables und tragbaren Elektronik. Zum Beispiel, Die 48-Ball-BGA im IC-Speicher in vielen tragbaren Geräten hat heute eine Größe von 8 mmx6mmx1mm (48mm3). Im Vergleich, Das gleiche Teil in einem CSP -Paket misst 3,7 mmx3,8 mmx0,5 mm (7mm3). Mit anderen Worten, Sie können das Volumen durch reduzieren 85%. Diese Einsparungen können verwendet werden, um den PCB -Bereich und die Dicke für tragbare Geräte zu reduzieren. Infolge, Die Nachfrage nach WLCSP -basierten Geräten von Wearables und Internet of Things (IoT) Die Hersteller sind nicht auf SRAM beschränkt, Aber es gibt eine neue Nachfrage.

UGPCB-LOGO

UGPCB-LOGO