Einführung: Industrielle Bedeutung und technische Herausforderungen von Via Filling

In 2023, der globale Leiterplatte Markt übertroffen $89.3 Milliarde (Prismark), mit der Überfüllung von Technologie, die kritisch beeinflusst 30% Ertragsschwankungen in 5G -Kommunikationsgeräten. Dieser Artikel analysiert thermodynamische Gleichungen und Prozessmatrizen, um anzuzeigen, wie sich über die Füllung auf die Signalintegrität und die thermische Zuverlässigkeit auswirkt.

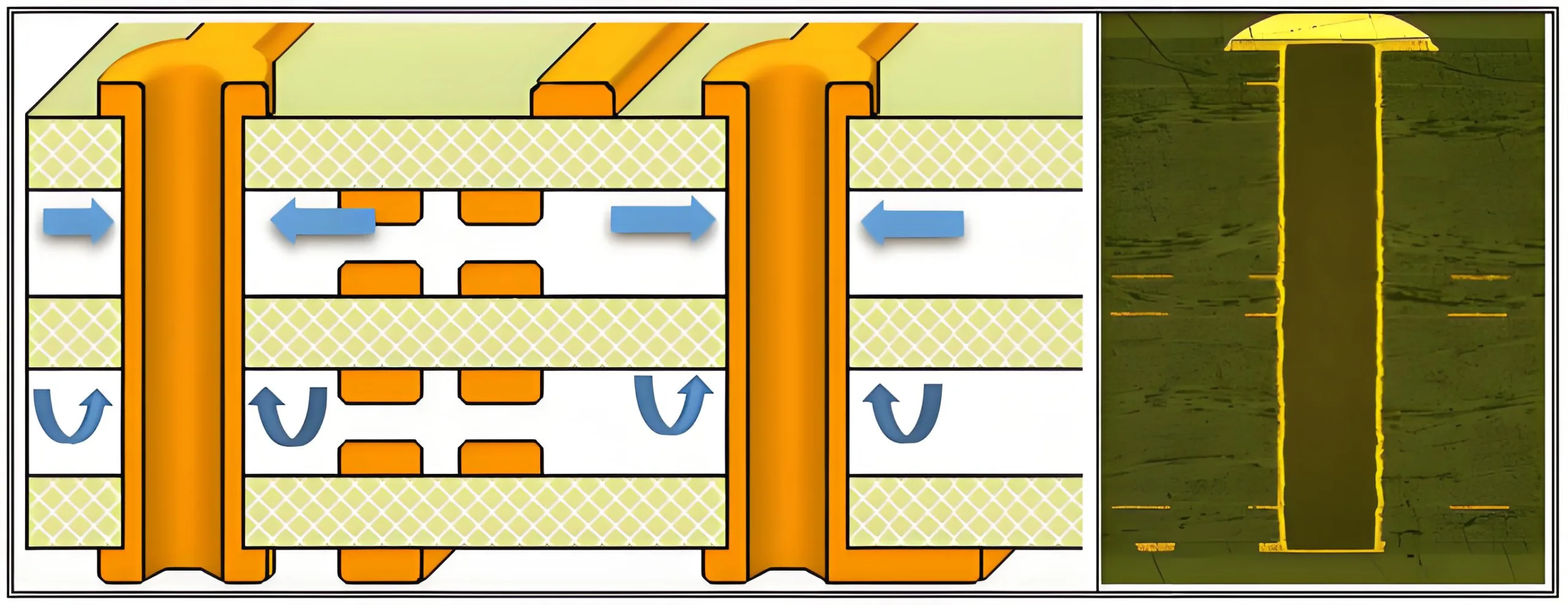

1. Über Füllungs -Technologie -Framework

1.1 Microvia Physik und Prozessfenster

Pro IPC-6012E, VIAS werden als leitende Löcher ≤ 0,70 mm definiert (28Mil). Das Fenster zum Ausfüllprozess folgt:

D = (K × t)/(σ × η)

Wo:

- D: Maximaler füllbarer Durchmesser (mm)

- T: Substrat tg (°C)

- A: Harzoberflächenspannung (mn/m)

- oder: Füllstoffviskosität (Pa · s)

- K: Prozesskoeffizient (0.02–0.05)

Für FR-4-Substrate (TG = 140 ° C), Löcher füllen >0.40MM erfordert Materialien mit σ<25Mn/M und η<120Pa · s.

2. Harzfüllungsphysik

2.1 Durch Tiefenschwelle begraben

Die Harzfüllung wird für vergrabene VIAS ≥ 0,8 mm aufgrund der Laminierungsflussdynamik obligatorisch:

P = (γ × cosθ)/(r × h)

Wo:

- P: Fülldruck (MPA)

- C: Prepreg -Oberflächenspannung

- th: Kontaktwinkel

- R: Über Radius

- H: Über Tiefe

Bei H≥0,8 mm, Standard -Laminierungsdruck (3–5mpa) Füllt keine Hohlräume, erfordert vakuumgestützte Harzfüllung.

2.2 Harz vs. Laminierungsfüllung: 6-Dimensionsvergleich

| Parameter | Harzfüllung | Laminierungsfüllung |

|---|---|---|

| Dicke Gleichmäßigkeit | ± 5% | ± 15% |

| Delaminierungsrisiko | <0.1% | 0.5–1,2% |

| Kosten | $0.35/dm² | $0.12/dm² |

| Mindestspurenbreite | 50μm | 75μm |

| Wärmezyklen | 3,000 | 1,500 |

| Signalverlust (@10ghz) | 0.15DB/Zoll | 0.25DB/Zoll |

3. Lötmaskenfüllungsprozess

3.1 Tintenflussmodell in der negativen Bildgebung

Lötmaskenfüllung folgt einer modifizierten Hagen-Poiseuille-Gleichung:

Q = (πr⁴δp)/(8μl) × (1 – e^(-T/t))

Mit Zeitkonstante t = mr²/(4C), erklären 50% Füllen Sie die Raten in halbgefüllten Vias bei der Expositionszeit t τ aus.

3.2 Fallstudie von Hasl Board Fehlern

Unbesetzte VIAS in 5G -Basisstation PCBs verursachten Blechperlen, modelliert durch die Arrhenius -Gleichung:

t_f = a × exp(EA/(kt))

Die Tests zeigten, dass MTBF von gefallen ist 10 Zu 2.3 Jahre bei 85 ° C/85%RH. Implementierung von 0,30 mm VIAS mit Lötmaskenöffnungen ≤(über Durchmesser +0,08 mm) Reduzierte Blech -Perlenfehler von reduzierten 12% Zu 0.7%.

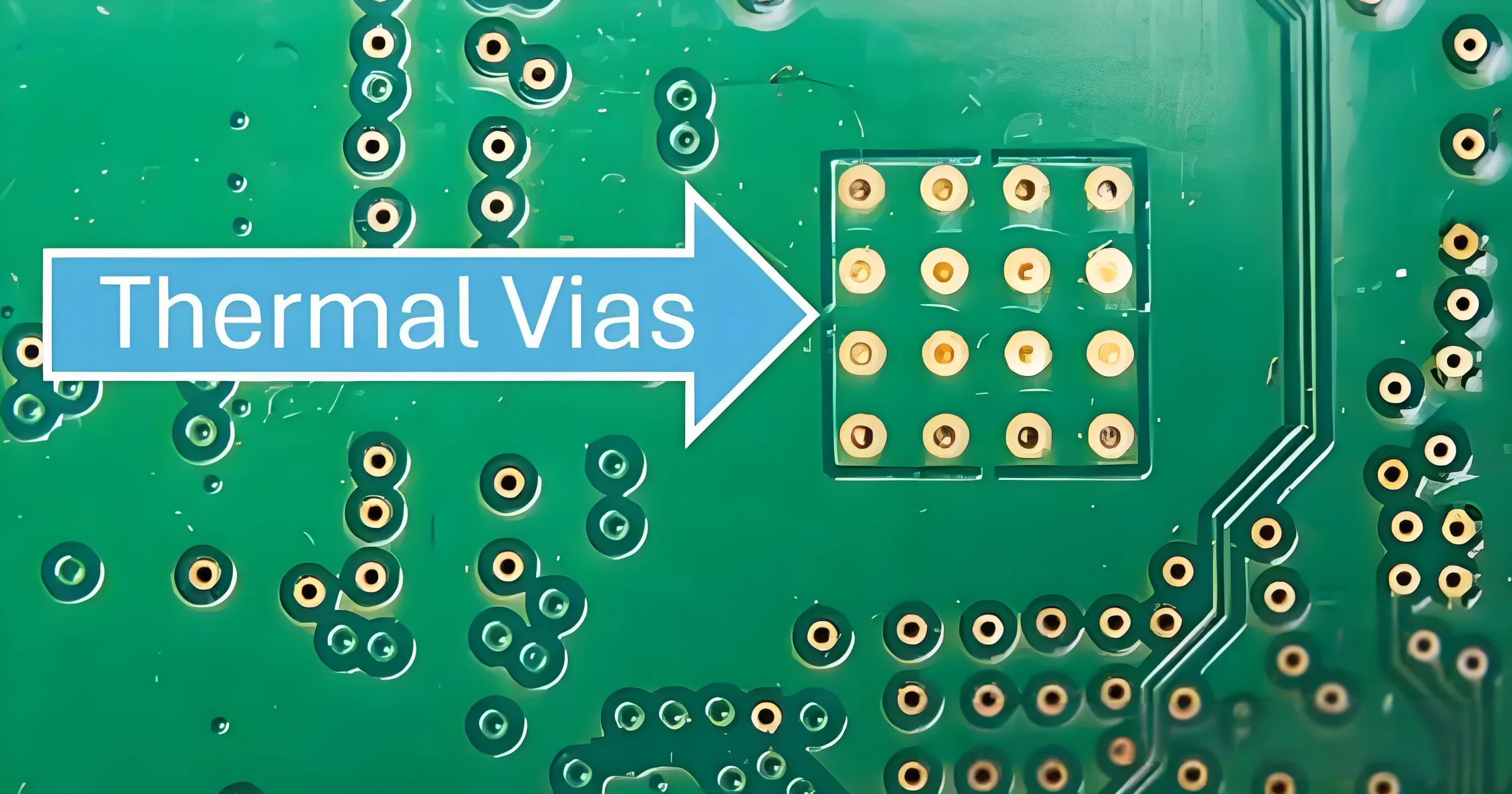

4. Fortgeschrittene durch Fülltechnologien

4.1 Leitfähige Füllung für die EMI -Abschirmung

Silberepoxidfüllung verbessert die Wirksamkeit der Abschirmung (Mit):

SE = 20log(1/(1-R)) + 10Protokoll(N)

Bei 80% Füllrate (P = 0,8), SE verbessert sich um 18 dB bei 1 GHz.

4.2 Plattierte Kupferfüllung für die Signalintegrität

Kupfer gefüllt durch Impedanz:

Z0 = (87/√ε_R)ln(5.98H/(0.8W+t))

Kupfersäulen verringern die Impedanzvariation von ± 15% auf ± 5%, Senkung von BER von 10 ° C auf 10⁻¹² bei 28 Gbit / s.

5. Prozessentscheidungsrahmen

Gesamtbetriebskosten (Tco) Analyse

- Unterhaltungselektronik: Lötmaskenfüllung bietet die niedrigste 5-Jahres-TCO an

- Automobil: Harz + Teilweise Kupferfüllung gewährleistet die Zuverlässigkeit

- Militär: Kupfersäulen optimieren die Signalintegrität

Abschluss

Über Füllung für 6G -Anwendungen

Als Terahertz-Frequenzen bedarf der Präzision unter 50 μm, Nano-Silver-Sintern tritt als Durchbruch auf. Das Beherrschen durch Füllungsphysik wird die nächste Generation fahren Hochfrequenz-Leiterplatte Innovation.

UGPCB-LOGO

UGPCB-LOGO