In der Elektronikherstellungsindustrie, die Ausbeute von PCBA (Montage von Leiterplatten) Die Verarbeitung wirkt sich direkt auf die Produktionskosten und die Wettbewerbsfähigkeit des Marktes aus. Forschung basierend auf IPC Internationale Standards weisen darauf hin, dass bis zu 80% Produktionsfehler können bereits in der Konstruktionsphase erkannt und optimiert werden.

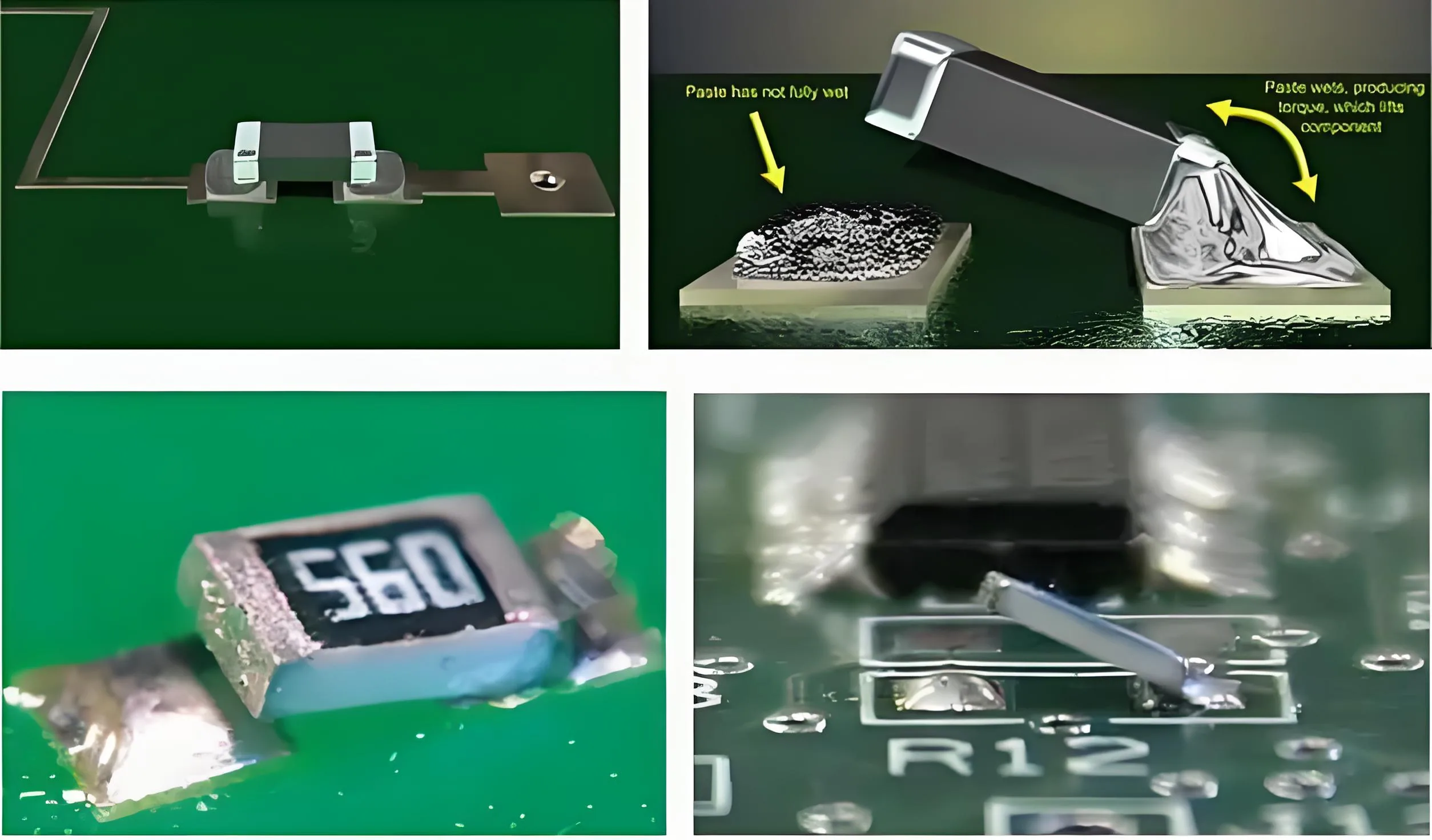

Im SMT (Oberflächenmontagetechnologie) Montageprozess, der Tombstoning-Defekt, bei dem sich ein Ende einer Chipkomponente vom Pad abhebt (Wie in Abbildung gezeigt 1)– ist eines der häufigsten Probleme. Es kommt häufig bei kleinen passiven Bauteilen vor, insbesondere 0402 Chip-Kondensatoren und Widerstände. Dieser Artikel bietet eine ausführliche Analyse, basierend auf der Versuchsplanung (DAMHIRSCHKUH) Methodik, des Zusammenhangs zwischen Schablonenfehlregistrierung und Tombstoning-Defekten, und schlägt praktische und effektive Lösungen vor.

-

Mechanismus und Auswirkungen von Tombstoning-Defekten

Die grundlegende Ursache des Tombstoning ist ein Ungleichgewicht bei der Lötspannung an den beiden Terminals einer Komponente. Wenn die Lötpaste schmilzt, Unterschiede in der Oberflächenspannung oder asynchronen Schmelzzeiten können dazu führen, dass die Komponente am Ende nach oben gezogen wird, wo die Lötpaste später schmilzt.

1.1 Bildungsmechanismus von Tombstonierungsfehlern

Während des Reflow -Lötens, Sowohl die oberen als auch die unteren Oberflächen der Chip -Komponente werden erhitzt. Allgemein, Das Pad mit dem größten freiliegenden Bereich erhitzt sich zuerst, Erreichen einer Temperatur über dem Schmelzpunkt der Lötpaste. Infolge, Das Ende der später benetzten Komponente wird oft durch die Oberflächenspannung des bereits molzenen Lötmittels am gegenüberliegenden Ende hochgezogen.

Lötspannungsbilanzformel:

F_net = f1 – F2 = γ_LV (cosθ₂ – cosθ₁) · L

Wo:

F_NET ist die Nettospannungskraft,

γ_LV ist die Flüssigkeitsvoroberflächenspannung,

θ ist der Kontaktwinkel,

L ist die Padlänge.

1.2 Faktoren für Tombstonierungsfaktoren beitragen

Basierend auf der Felddatenanalyse, Tombstoning -Defekte werden hauptsächlich von den folgenden Faktoren beeinflusst:

-

PCB-Design Faktoren (30%): Unregelmäßige Blockgröße Design und suboptimales Layout

-

Material Faktoren (25%): Schlechte Lötbarkeit von Komponenten, Oxidierte Kündigungen

-

Prozessfaktoren (45%): Lötpaste Fehlregistrierung, Unzureichende Platzierungsgenauigkeit, Unsachter Reflow -Löttemperaturprofil

-

DOE Experimental Design und Methodik

Um das durch Fehlregistrierung für einen Dek -Schablonen -Drucker verursachte Tombstoning -Problem anzugehen, das technische Team bei UGPCB entwarf ein strenges DOE, um die optimale Kombination von Prozessparametern zu identifizieren.

2.1 Versuchsziele und charakteristische Wertdefinition

Charakteristischer Wert: Lötpaste Fehlregistrierung (Einheit: mm)

Charakteristischer Typ: Kleiner

-

Messgeräte: AOI (Automatisierte optische Inspektion)

-

Messmethode: Für jede Kombination, messen 10 Bretter. An jedem Brett, Messen Sie die Fehlregistrierung von Lötpaste auf fünf 0402 Komponentenpolster, und nehmen Sie den Höchstwert als Fehlregistrierung für diesen Vorstand.

-

Berechnungsmethode: Der durchschnittliche Fehlregistrierungswert über die 10 Boards werden als Fehlregistrierungswert für diese Parameterkombination angesehen.

2.2 Auswahl fester und experimenteller Faktoren

Feste Faktoren:

-

Boardtyp: Rock Lake (Intel)

-

Produktionslinie: Linie 14

-

Schablone: Die gleiche Schablone verwendet überall

-

Rang: Das gleiche Rakel -Set, das überall verwendet wird

-

Mechanischer Zustand: Die Ausrüstung hat eine Wartung unterzogen

Experimentelle Faktoren:

-

Faktor a: Vakuumhaltezeit (Kontrolliert Vakuumkraftpegel durch Anpassung der Haltezeitdauer)

-

Faktor b: Förderbahnbreite (Stellt die Breite an, um sie zu sichern Leiterplatte und Bewegung verhindern)

-

Faktor c: Druckdruck

-

Faktor d: Druckgeschwindigkeit

-

Faktor e: Abstand zwischen Treuhandmarken

-

Experimentelle Ergebnisse und Analyse

Das Experiment wurde in zwei Phasen durchgeführt: Die erste Stufe wurde nach signifikanten Faktoren untersucht, und die zweite Stufe optimierte die Parameterkombination.

3.1 Schlussfolgerungen der ersten Stufe

Signifikante Faktoreffekte: A, ANZEIGE (Interaktion), CD (Interaktion), E

Faktoren, die für Stufe zwei ausgewählt wurden: A, C, D, E

Hoch signifikante Faktoren: A, ANZEIGE, CD

Unerwarteter Befund: Faktor b (Förderbahnbreite), anfangs als sehr einflussreich angesehen, zeigte keinen signifikanten Effekt. Die meisten signifikanten Effekte waren Interaktionseffekte.

3.2 Stadium zwei Experiment- und ANOVA -Analyse

ANOVA -Ergebnisse zeigten, dass die Faktoren a, C, und D waren in der zweiten Stufe nicht signifikant. Dies deutet darauf hin, dass die beobachteten Hauptvariationen auf zufällige Fehler zurückzuführen waren, Die Angabe der Parameteroptimierung hatte ein nahezu optimales Niveau erreicht.

-

Optimale Prozessparameter und Standardisierung

Basierend auf den experimentellen Ergebnissen, Die optimalen Produktionsprozessparameter wurden bestimmt:

Tisch 1: Vergleich der Prozessparameter vor und nach der Verbesserung

| Parameter | Vorverbesserung | Nachverbesserung | Ändern |

|---|---|---|---|

| Druckdruck | 6.0 Kg | 5.4 Kg | Verringern 10% |

| Druckgeschwindigkeit | 40 MM/Sek | 50 MM/Sek | Zunahme 25% |

| Vakuumhaltezeit | 0.4 Sek | 0.4 Sek | Keine Änderung |

| Kennzeichenentfernung | 361.9 | 361.9 | Keine Änderung |

| Förderbahnbreite | 244.3 | 244.3 | Keine Änderung |

Begründung für ausgewählte Parameterkombination:

-

Faktor a (Vakuumhaltezeit): Ausgewählt 0.4 Sec im Bereich von 0,4 ~ 0,8 Sekunden, um den Druckerzeitverlust zu minimieren.

-

Faktor c (Druckdruck): Wählte die niedrigere Ebene von aus 5.4 Kg, Als übermäßiger Druck kann Schablonendeformation und dickere Lötpaste -Ablagerung verursachen.

-

Faktor d (Druckgeschwindigkeit): Ausgewählt 50 MM/Sek, Da höhere Geschwindigkeiten zu einer schlechten Lötpaste -Freisetzung führen können.

-

Leistungsbewertung und Kostenanalyse

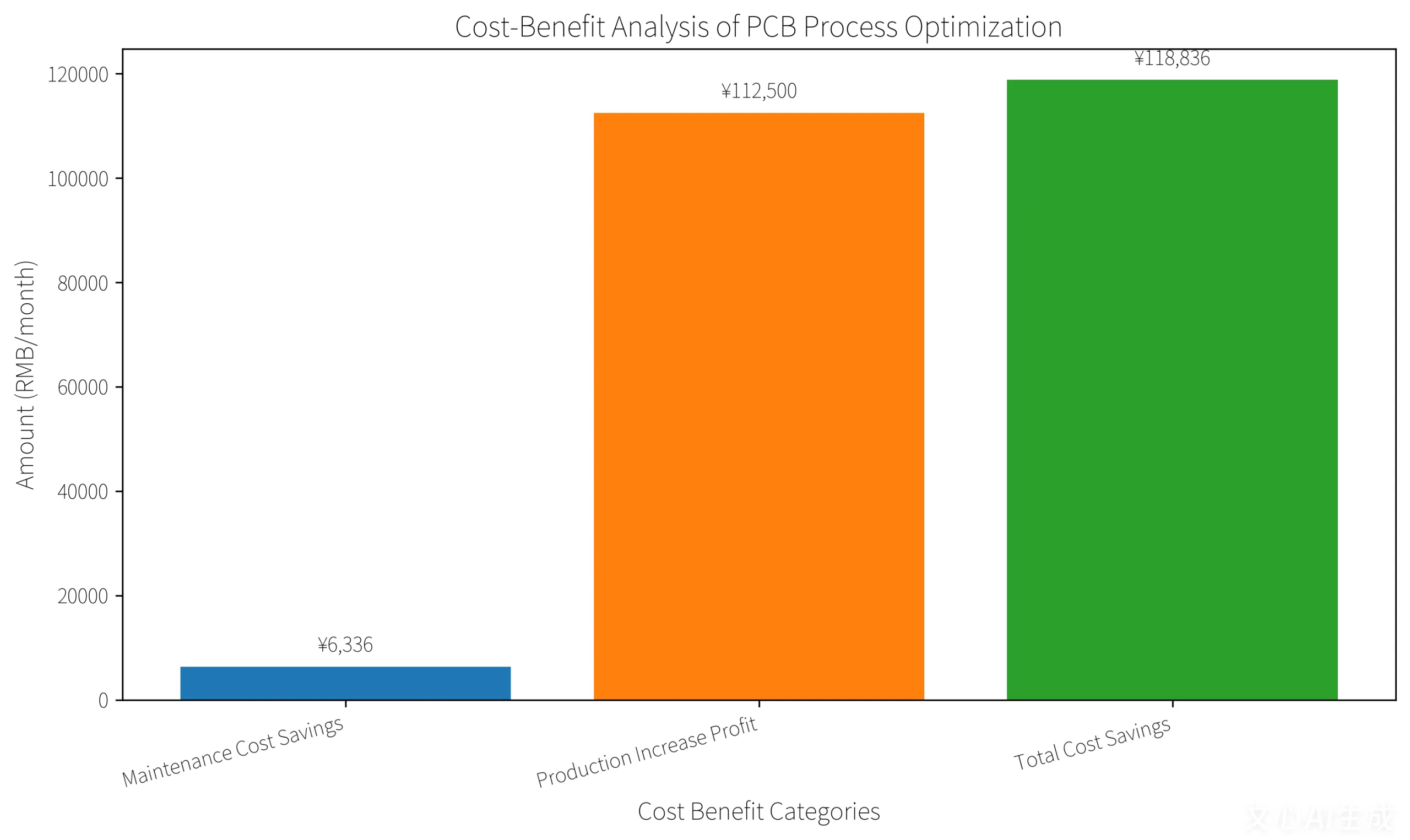

Nach der Optimierung der Prozessparameter, Es wurden erhebliche wirtschaftliche Vorteile und Qualitätsverbesserungen erzielt:

5.1 Qualitätsverbesserungsergebnisse

Die Tombstonierungsfehlerrate nahm von ab 29% Zu 18%, ein 11 prozentuale Punktreduzierung. Berechnet nach IPC-7912-Standards, Der Prozesskapazitätsindex CP verbesserte sich von 0.89 Zu 1.32, und CPK verbesserte sich von 0.72 Zu 1.08.

5.2 Wirtschaftliche Nutzenberechnung

-

Kosteneinsparungen überarbeiten: 66 weniger defekte Boards pro SMT -Linie pro Woche. Bei 2 Protokoll -Überarbeit pro Brett:

Arbeitseinsparung = 66 Bretter × 2 min/board × 8 Linien × 4 Wochen = 4224 min/Monat

Kosteneinsparungen = 90 RMB/Stunde × (4224 / 60) = 6,336 RMB/Monat -

Output erhöht den Gewinn: Vorverbesserung, Die Druckeranpassungen zur Fehlregistrierung dauerten ca.. 5 min/line/tag:

Arbeitseinsparung = 5 min/Tag × 30 Tage × 8 Linien = 1200 min/Monat

Ausgangserhöhung Gewinn = (1200 / 60 / 24) × 1500 Bretter/Tag × 90 Rmb/board = 112,500 RMB -

Monatliche Kosteneinsparungen = 6,336 + 112,500 = 118,836 RMB

-

Aufbau eines Qualitätskontrollsystems in Vollprozess

Tombstoning -Probleme gründlich anzugehen, Es ist wichtig, ein umfassendes Qualitätssicherungssystem zu etablieren, das alle Phasen abdeckt: Eingehende Materialien → In-Prozess-Produktion → Inspektion des fertigen Produkts → Versagen nach dem Verkauf.

6.1 Eingehende Qualitätskontrolle (IQC)

IQC ist der erste Kontrollpunkt. Wichtige Rohstoffe wie die Kupferfolie von Leiterplatten und Substrate Erfordernden Aussehen und dimensionale Probenahmeprüfung: Kupferfolienoberfläche muss frei von Oxidation sein, Pinholes, und Kratzer; Die Toleranz der Substratdicke muss den Standard ± 0,05 mm erfüllen.

6.2 Qualitätskontrolle in Prozess (IPQC)

IPQC umfasst den gesamten PCB -Herstellungsprozess, mit “Qualitätskontrollpunkte” Nach jedem Schlüsselvorgang. Nach der inneren Schicht Bildgebung, Überprüfen Sie die Spurenbreite/den Abstand und die Ätzung der Gleichmäßigkeit; Nach Laminierung, Verwenden Sie die Röntgeninspektion, um nach Zwischenschichthohlräumen und Fehlregistrierung zu überprüfen; Nach dem Übernehmen, Verwenden Sie Kupferdicke, um Loch und Oberflächenkupferdicke zu messen.

6.3 Endgültige Qualitätskontrolle (FQC)

FQC ist der letzte Test vor dem Versand, Drei Hauptabmessungen abdecken: Aussehen, elektrische Leistung, und Zuverlässigkeit. Für das Aussehen, Verwenden Sie eine Kombination aus manueller und AOI -Inspektion; elektrisch, durchführen 100% Flugsonde oder Nagelstests, um keine Öffnungen oder Shorts zu gewährleisten; für Zuverlässigkeit, Führen Sie Umwelttests anhand der Kundenanforderungen durch.

-

Empfehlungen zur Optimierung von PCB -Designoptimierung

Über die Prozessoptimierung hinaus, Die PCB -Designoptimierung ist entscheidend für die Vorbeugung von Tombstoning -Defekten.

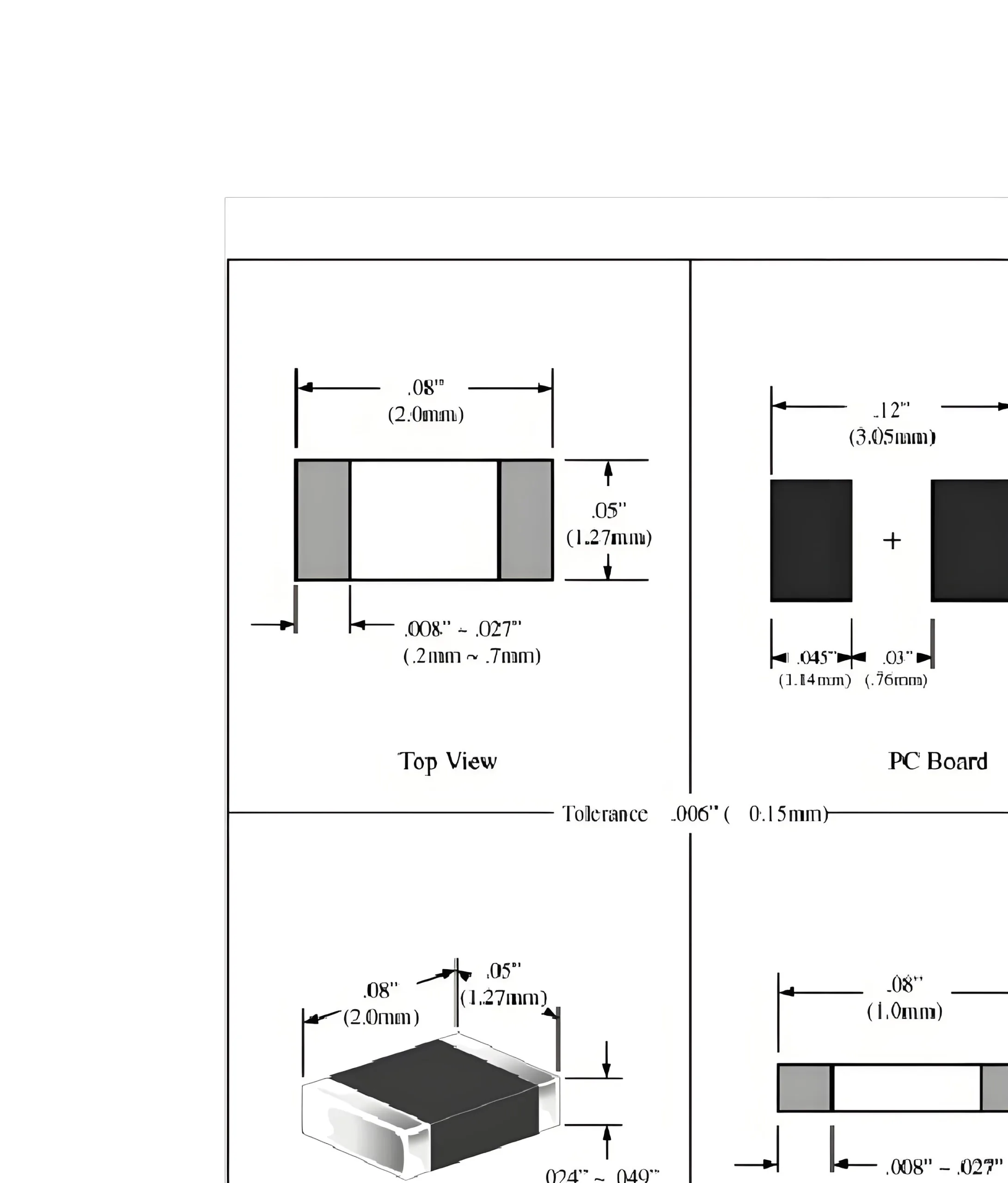

7.1 Pad -Designstandards

Optimieren. Vermeiden Sie Szenarien, in denen die Kante des Pads (Gerade) bildet einen Benetzungswinkel von mehr als 45 °. Gemäß den IPC-7351-Standards, für 0402 Komponenten, Der Padabstand sollte innerhalb von 0,35 ± 0,05 mm gesteuert werden, und die Padbreite sollte 0,5 ± 0,05 mm betragen.

7.2 Layout -Optimierungsstrategie

Schlechtes Komponentenlayout kann zu signifikanten Größenschwankungen zwischen führen Komponenten Auf der Leiterplatte. Während des Reflow -Lötens, Dies führt zu übermäßigen Temperaturunterschieden, ungleichmäßige Erwärmung auf beiden Seiten einer Komponente, und Grabstonierung. Vermeiden Sie es, kleine Komponenten neben Hochleistungsgeräten während des Designs zu platzieren, um eine gleichmäßige Wärmeverteilung zu gewährleisten.

-

Follow-up-Aktionen und kontinuierliche Verbesserung

Die folgenden Maßnahmen wurden durchgeführt, um die Nachhaltigkeit der Verbesserungen sicherzustellen:

8.1 Kontinuierliche Überwachung und statistische Analyse

Sammeln Sie kontinuierlich Tombstoning -Ertragsdaten für 30 Tage, Verwenden Sie Kontrolldiagramme zur Überwachung, und bestätigen Sie die anhaltende Verbesserungseffektivität. Daten aus Oktober zeigten eine signifikante Verbesserung, mit fortgesetzten positiven Auswirkungen auf die Fehlregistrierung.

8.2 Kausalitätsanalyse- und Kontrollstandards

Basierend auf Verbesserungsergebnissen, Studieren Sie die kausale Beziehung zwischen Fehlregistrierung und Grabstonierung, Kontrollstandards festlegen, und integrieren Sie sie in das tägliche Management. Implementieren a “Quality Rückverfolgbarkeitscode” Für jede PCB, Aufzeichnung von Informationen wie Rohmaterialstapel, Produktionsausrüstung, Inspektionsdaten, und Betreiber.

8.3 Expansions- und Technologieübertragung

Erweitern Sie die Ergebnisse dieses DOE auf andere Produktionslinien und Produktmodelle. Erstellen Sie eine Prozessparameterdatenbank, Standardisieren Sie Parameter für bewährte Lösungen, und verkürzen 24 Stunden bis 3 Std..

-

Schlussfolgerung und Ausblick

Verwenden der DOE -Methodik, Wir haben erfolgreich wichtige Prozessparameter identifiziert, die sich mit einer Fehlregistrierung der Lötpaste auswirken und die Tombstoning -Defektrate von reduziert haben 29% Zu 18% durch Parameteroptimierung. Dies erzielt monatliche Kosteneinsparungen von ca. 118.836 Yen, Übersetzung zu annualisierten Einsparungen von etwa 1,426 Millionen Yen.

Blick nach vorn, Wir werden die Prozessforschung weiter vertiefen, Erforschen Sie die Anwendung der AI -Technologie in der Optimierung der Prozessparameter, Erstellen Sie intelligente Prozessoptimierungssysteme, und eine kontinuierliche Verbesserung der Produktqualität und der Produktionseffizienz erreichen.

Für Elektronikhersteller mit neuen Produkteinführungsbedürfnissen, Es ist ratsam, einen One-Stop-Lösungsanbieter wie UGPCB auszuwählen, Dies integriert das PCB -Design, Herstellung, Leiterplatte, Und PECVD Dienstleistungen. Wir betrachten potenzielle Probleme während der PCB- und PCBA -Prozesse aus der Entwurfsphase, Führen Sie verschiedene Simulationstests durch, und implementieren Sie ein Qualitätskontrollsystem in vollem Prozess von eingehenden Materialien bis hin zu Tests und Verpackungen, Gewährleistung der Produktqualitätsstabilität und -konsistenz.

UGPCB-LOGO

UGPCB-LOGO