ITEQ IT-158 PCB-Plattenmaterial

Schlüsselleistungsparameter & Technische Vorteile

ITEQ IT-158 Laminat entsteht als erstklassige Wahl für High-End-PCB Herstellung durch außergewöhnliche technische Spezifikationen:

Thermische Zuverlässigkeit

-

Tg: 155°C (Gewährleistet die strukturelle Stabilität während der leitfreien Lötung)

-

T-288: >30 Sekunden bei 288 ° C. (Überlegener thermischer Schockwiderstand)

-

TD-5%: 345°C (verhindert die Delaminierung unter extremen Bedingungen)

Mechanische Stabilität

-

Z-Achse CTE: 40ppm/° C. (3.3% Expansion von 50-260 ° C.)

-

Schalenstärke: ≥8lb/Zoll (Kupferverkleidete Bondintegrität)

-

Wasseraufnahme: 0.08% (behält die elektrische Stabilität in 85% RH -Umgebungen)

Hochfrequenzsignalübertragungseigenschaften

Dielektrische Leistung bei 10 GHz

-

Dk: 4.0 ± 0,05

-

Df: 0.018

*(Ideal für 5G/MMWAVE -Anwendungen mit 0,15 dB/Zoll Insertionsverlustreduzierung)*

Typische Anwendungsszenarien

5G Kommunikationsinfrastruktur

-

Basisstation Antennen

-

Optische Transceiver

Kfz -Elektronik

-

Adas Radarsysteme (AEC-Q200 kompatibel)

-

ECU -Kontrollmodule

Industrieautomatisierung

-

Servo fährt (10,000HR MTBF bei 105 ° C)

-

Power Wechselrichter

Unterhaltungselektronik

-

Smartphone -HF -Module

-

Laptop Motherboard HDI -Designs

PCB -Materialauswahl Workflow

Phase 1: Anforderungenanalyse

-

Betriebstemperaturbereich: Tmax +20 ° C Rand

-

Signalfrequenzschwelle: ≥1 GHz kritisch

-

Umweltbewertung: IP67 Compliance

Phase 2: Vergleichende Bewertung

| Parameter | Iteq it-158 | Konkurrent a | Konkurrent b |

|---|---|---|---|

| Tg (°C) | 155 | 140 | 130 |

| DF @10GHz | 0.018 | 0.025 | 0.032 |

| UL -Zertifizierung | 94V-0 | 94Hb | 94V-1 |

Phase 3: Zuverlässigkeitsvalidierung

-

PCT -Test: 121° C/100%RH/2ATM × 96 Stunden

-

Wärmespannung: 3× Lötmittel dips bei 288 ° C

-

CAF -Widerstand: IPC-TM-650 2.6.25 konform

Designoptimierungsstrategien

Stackup -Konfiguration

-

Hybrid -Dielektrikum (≤ 5% Dicke Toleranz)

-

Begraben VIAS für das thermische Management

Impedanzkontrolle

-

Microstrip -Linien -Toleranz: ± 10%

-

Differentialpaarabstand: 3× dielektrische Höhe

Herstellungsprozess

-

Bohren: Back-Drilling mit ≤ 0,15 mm Stub

-

Oberflächenbeschaffung: Enepig bevorzugte (In:3-5μm, Au:0.05-0.1μm)

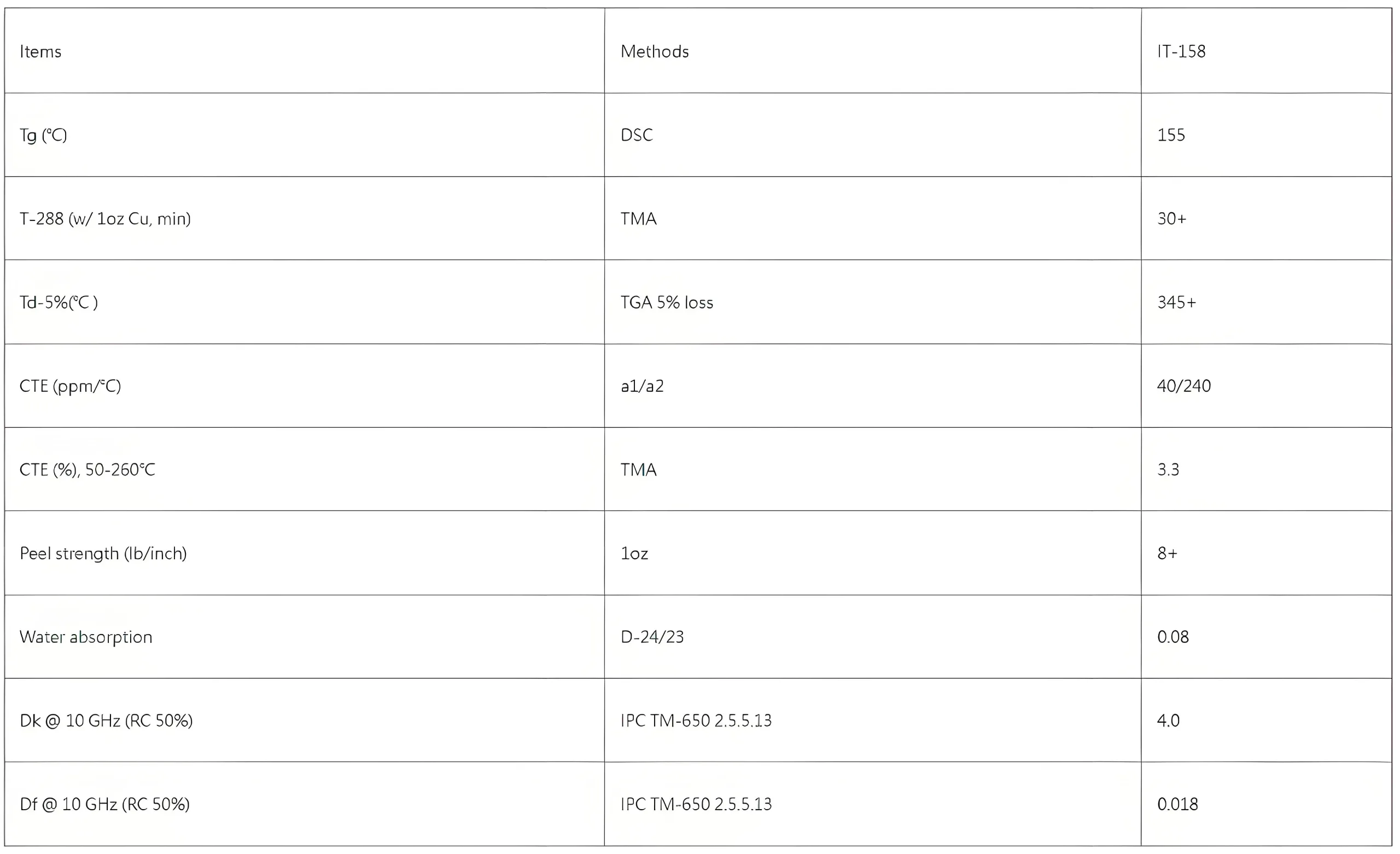

ITEQ IT-158 PCB-Substrat-Parametertabelle

UGPCB-LOGO

UGPCB-LOGO

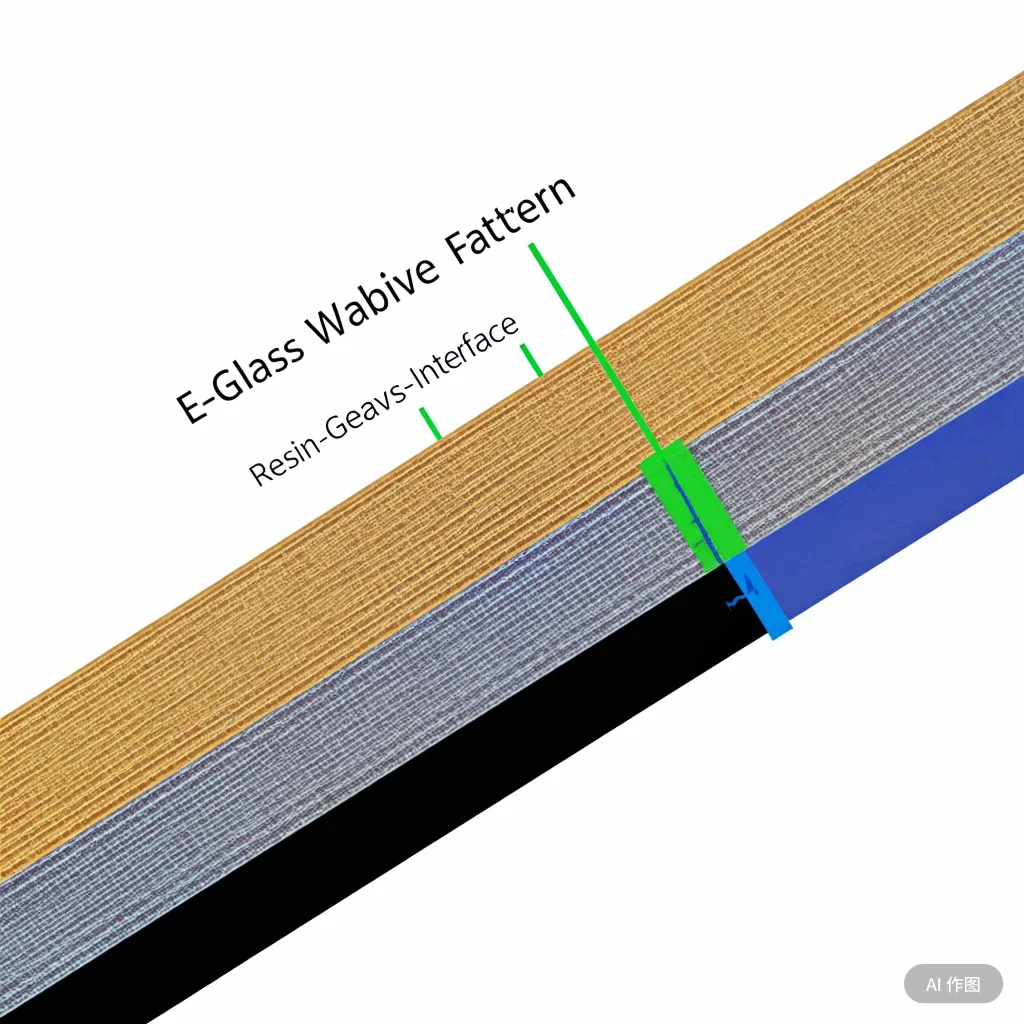

Wirklich informative und fantastische anatomische Struktur des Themas, Das ist jetzt benutzerfreundlich (:.