Les puces semi-conductrices servent de “cerveau” de l'ère numérique, tandis que l'emballage de puce agit comme leur protecteur “armure” et “réseau neuronal.” Au-delà du blindage en silicium fragile meurt, il permet une gestion thermique critique, connectivité électrique, et transmission du signal. Des forfaits volumineux à un trou aux solutions de niveau à la plaquette ultra-mince, L'évolution des emballages a motivé la miniaturisation de l'électronique et l'amélioration des performances - une saga technologique monumentale.

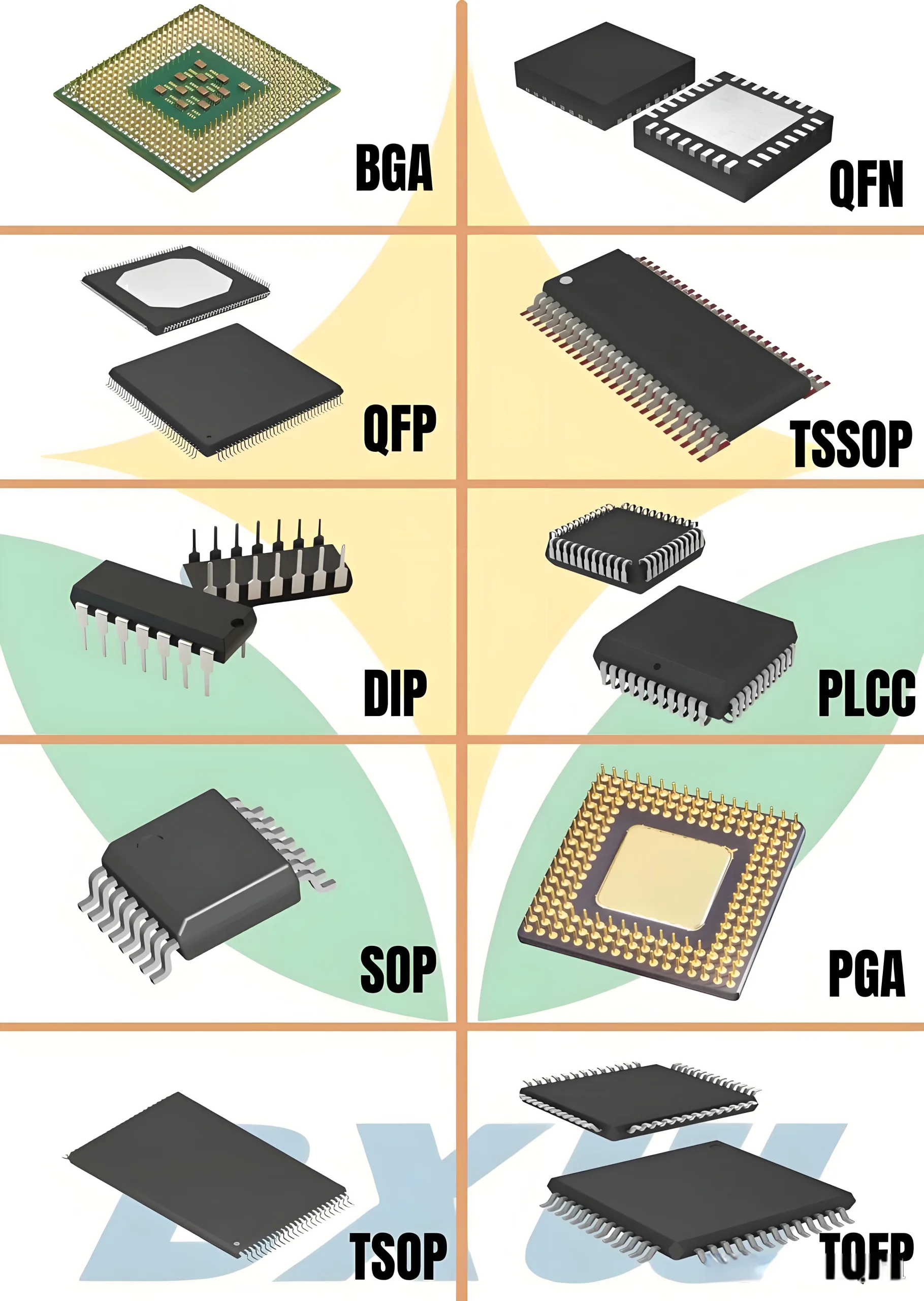

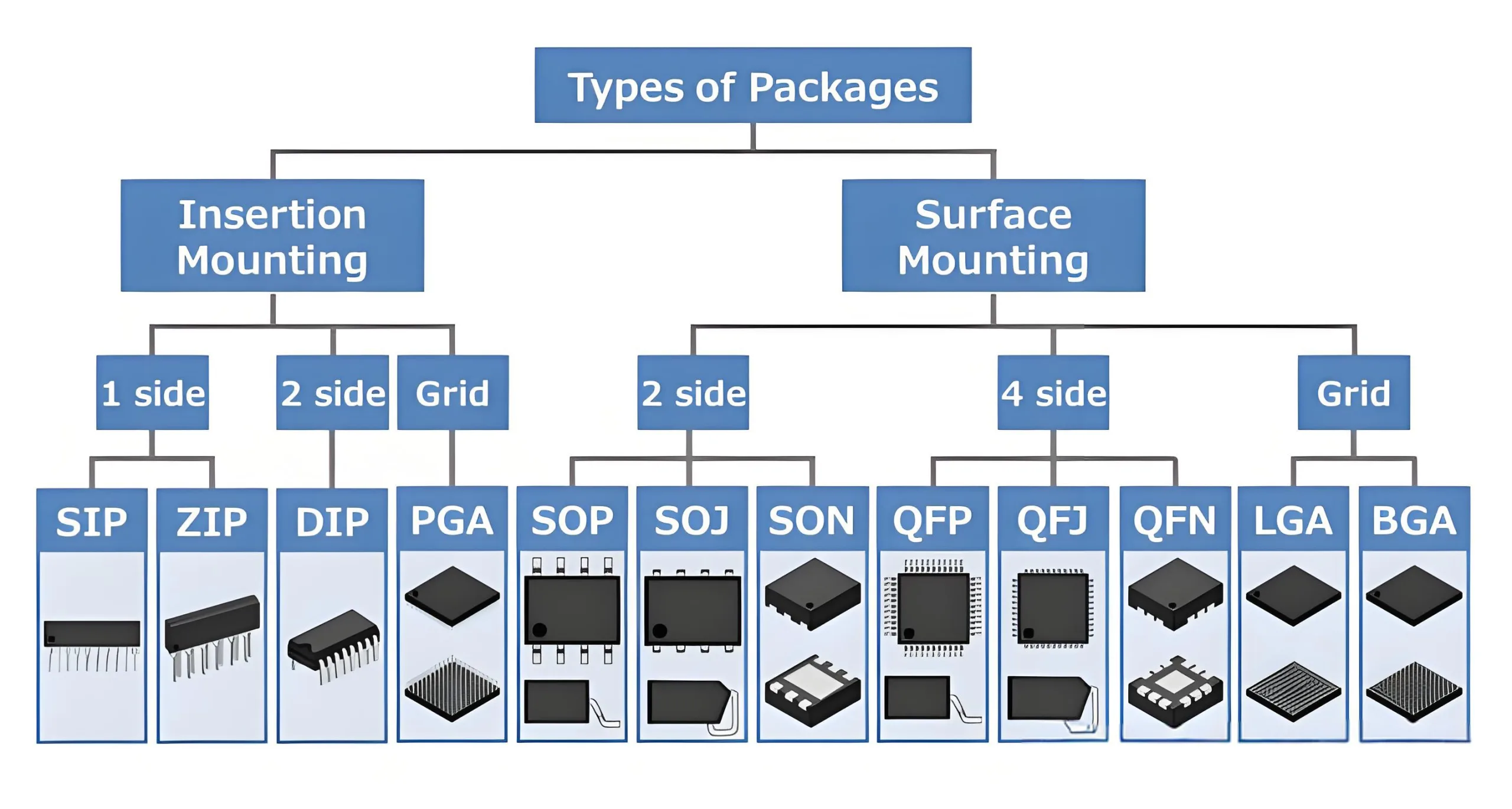

Classifier les technologies d'emballage

Par méthode de montage

-

Emballage à travers (Tht):

Broches insérées dans PCB plaqué à travers les trous pour la soudure. Représente une technologie de génération précoce. -

Technologie de montage de surface (CMS):

Composants directement soudés sur des coussinets PCB. Permet une densité plus élevée et un assemblage automatisé.

Par configuration d'épingle (Progression de la densité)

Row → Dual-Row → Quadage → Area-Array

L'ère à travers

Faire / à: Fondements de composants discrets

-

Diode DO-41: Ø2,7 mm × 5,2 mm

-

Transistor à 220: Poignées ≤50W Dissipation de puissance

-

Résistance thermique: R.<sous>et</sous> = (T<sous>J</sous> – T<sous>un</sous>)/P.

Où R.<sous>et</sous> = résistance thermique à la jonction à ambiance

Sip / zip: Innovations uniques en ligne

-

SIROTER: 3-16 épingles, Effectif pour les résistances / diodes à faible puissance

-

FERMETURE ÉCLAIR: 40% densité de broches plus élevée que SIP via la disposition des broches en zigzag

-

Applications: Modules de mémoire précoce, régulateurs de tension

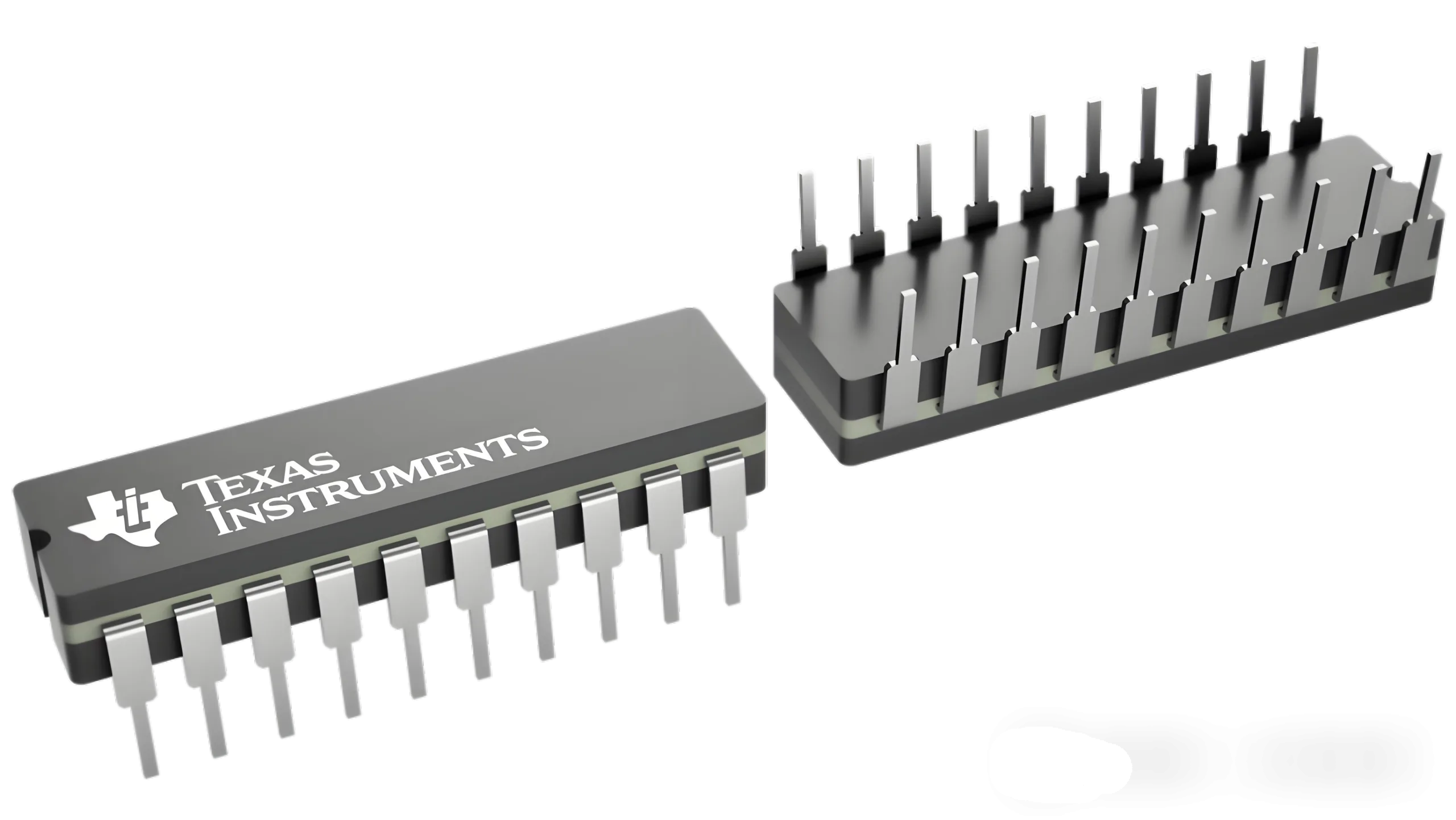

TREMPER: La révolution IC

-

Tangage d'épingle: 2.54mm (0.1″) standard

-

1980part de marché: >70% d'emballage IC

-

Performance thermique:

Plongeon en céramique: 20-30 W / M · k conductivité

Trempette en plastique: 0.2-0.3 W / m · k

PGA: Pionnier informatique haute performance

-

Densité d'épingle: 3× plus élevé que la trempette

-

Applications: Intel 80386/80486 Processeurs

-

Force d'insertion: 30-100 Newtons

La révolution SMT

Gazon / sot: Miniaturisation des composants discrets

-

SOD-323: 1.7mm × 1,25 mm

-

Résistance thermique SOT-23: ~ 250 ° C / W

-

Profil de reflux: Tempé de pointe 235-245 ° C

Mèches de goéland: Famille SOP

-

Évolution de pas d'épingle:

1.27mm (AMADOUER) → 0,8 mm (Ssop) → 0,65 mm (Tssop) -

Packages dérivés:

SOP → SSOP → TSOP → TSSOP → VSSOP -

Amélioration thermique: HSSOP réduit la résistance thermique par 40%

Configuration J-LEAD: Observation

-

Résistance mécanique: 30% résistance aux contraintes plus élevée

-

Limitation électrique: 0.8-1.2Inductance parasite du NH

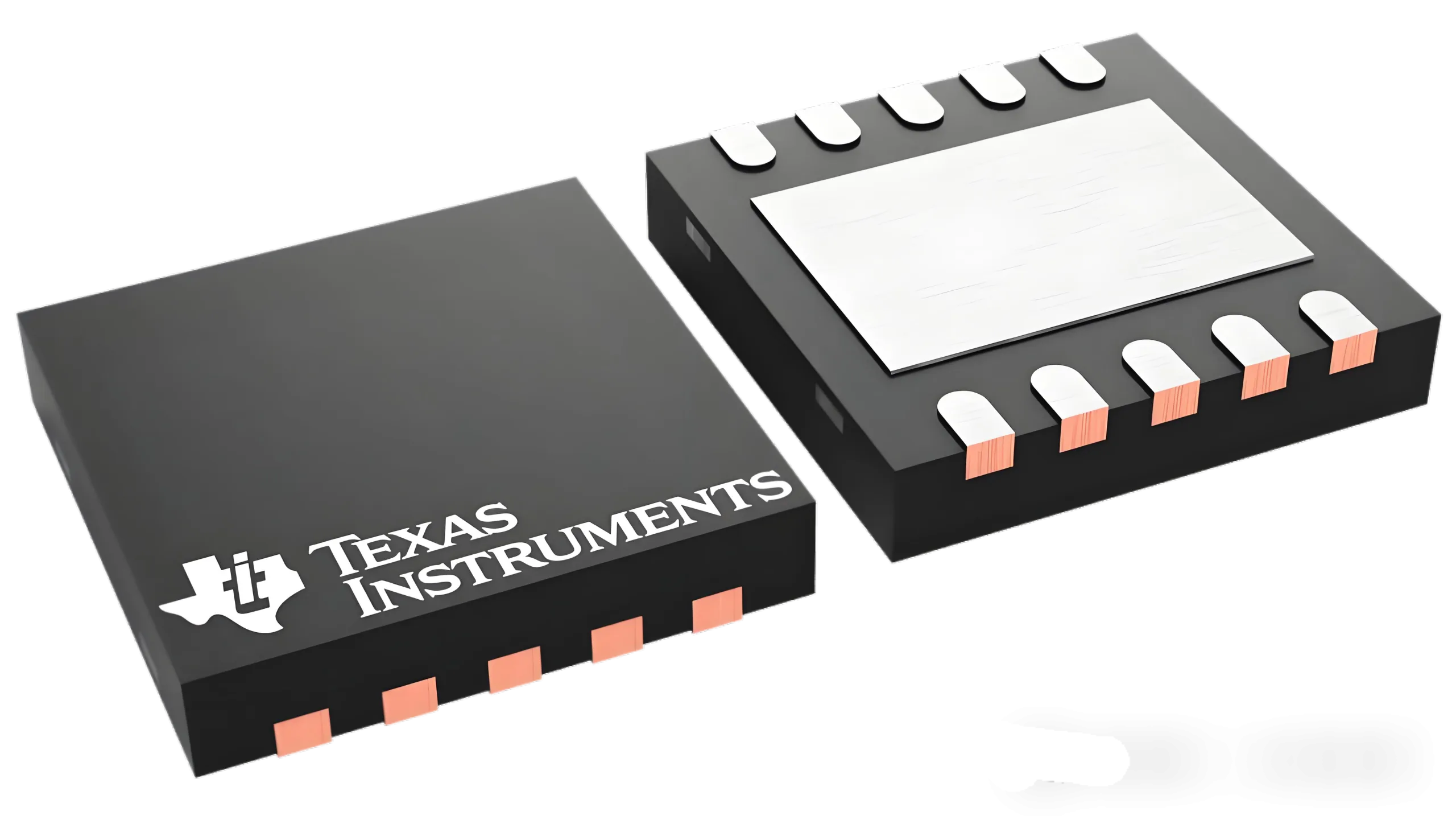

Percée sans plomb: Fils / DFN

-

Efficacité spatiale: >50% Amélioration par rapport à SOP

-

Performance thermique: 15° C / W avec des coussinets thermiques

-

Limite de miniaturisation:

X2SON: 0.6mm × 0,6 mm × 0,32 mm

Physique derrière la miniaturisation

Trois défis de base régissent la mise à l'échelle du package:

-

Gestion thermique:

Q = haΔt

Taille réduite (↓ A) exige un coefficient de convection plus élevé (↑ H) -

Contrôle des contraintes thermiques:

S = ertht

Où CTE (un) L'intégrité induit le stress -

Intégrité du signal:

Inductance de plomb * l ≈ 2L(LN(2l/d)-1) NH *

La miniaturisation réduit l'inductance par 30%

Frontière suivante: Emballage avancé

Comme X2SON frappe des échelles de 0,6 mm, L'innovation passe à:

-

3D Emballage: Intégration verticale compatible TSV

-

Intégration hétérogène: Assemblage de matrices à nœuds multiples

-

Photonique: Co-conception de Silicon Photonics

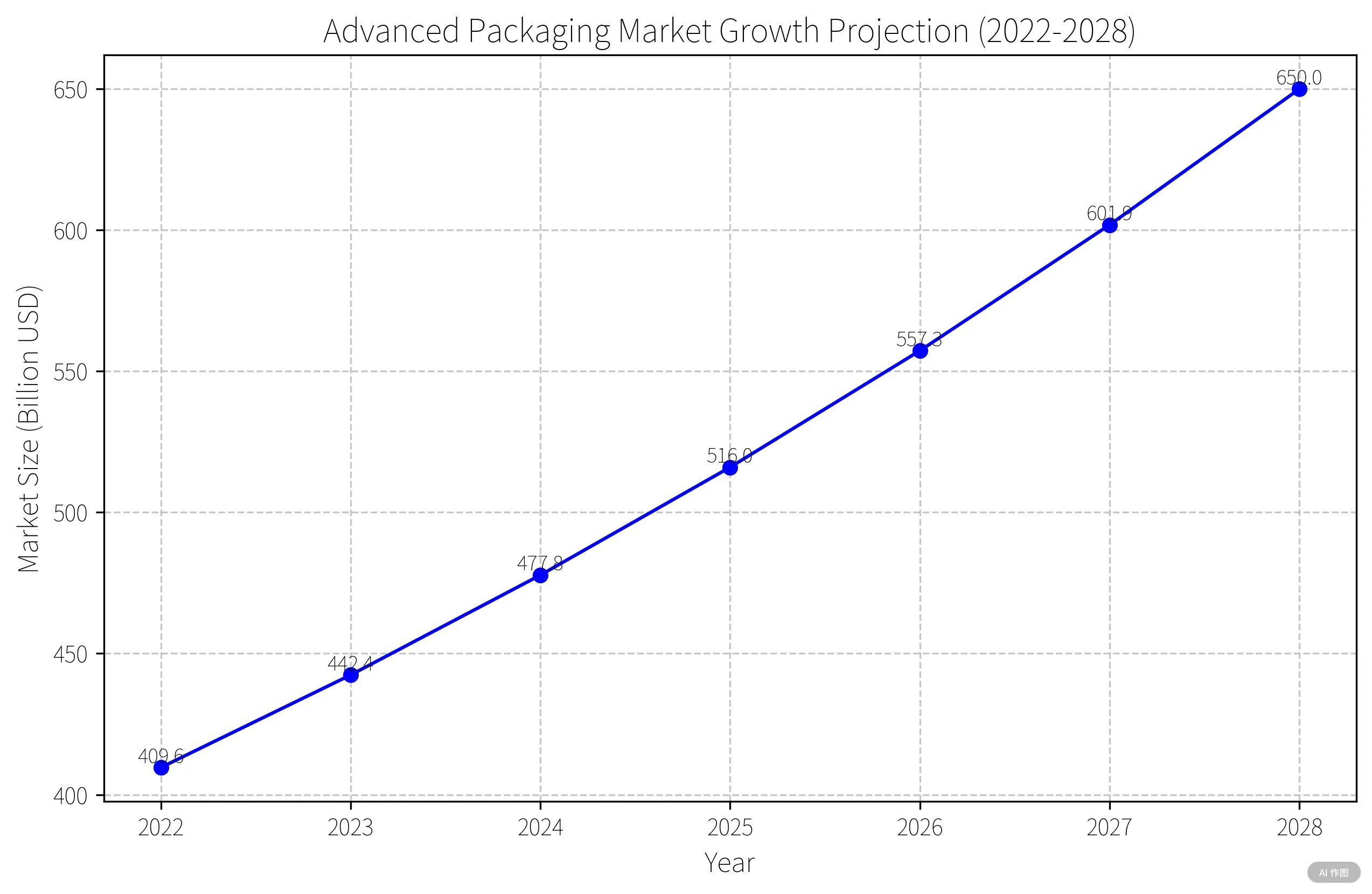

Prévisions du marché (Yole Développement):

8% CAGR à travers 2028 → Marché de 65 milliards de dollars

L'emballage définit désormais de manière critique les performances du système - bien au-delà de la simple protection.

Conclusion

De la hauteur de 2,54 mm de Dip à l'empreinte de 0,6 mm de X2SON, Avancement d'emballage redéfinir en continu l'électronique. Chaque smartphone mince et appareil 5G s'appuie sur ces innovations invisibles. Avec l'IA et l'informatique quantique émergeant, L'emballage de puce continuera à repousser les limites à l'échelle nanométrique.

*Suivant en série:

Technologies BGA / CSP / WLCSP

3D Emballage & Interconnexion TSV

Science des matériaux d'emballage avancé

Restez à l'écoute!*

LOGO UGPCB

LOGO UGPCB