PCBA 표면 실장 조립 과정에서, 다양한 전자 부품이 자주 고장납니다.. 오늘, 3A 선형 레귤레이터의 고장 분석에 대한 사례 연구를 공유합니다., 표면 너머를 살펴보고 결함을 빠르게 식별하는 방법을 설명합니다..

1) 칩 오류 설명: Vin이 접지로 단락되었습니다..

Vin이 접지로 단락되었습니다..

2) 장치 고장 분석: 칩이 EOS를 경험했습니다. (전기적 과잉 스트레스) Vin을 접지로 단락시킨 IV 테스트를 통해 확인된 오류.

IV 테스트를 통해 Vin과 접지 단락이 확인되었습니다..

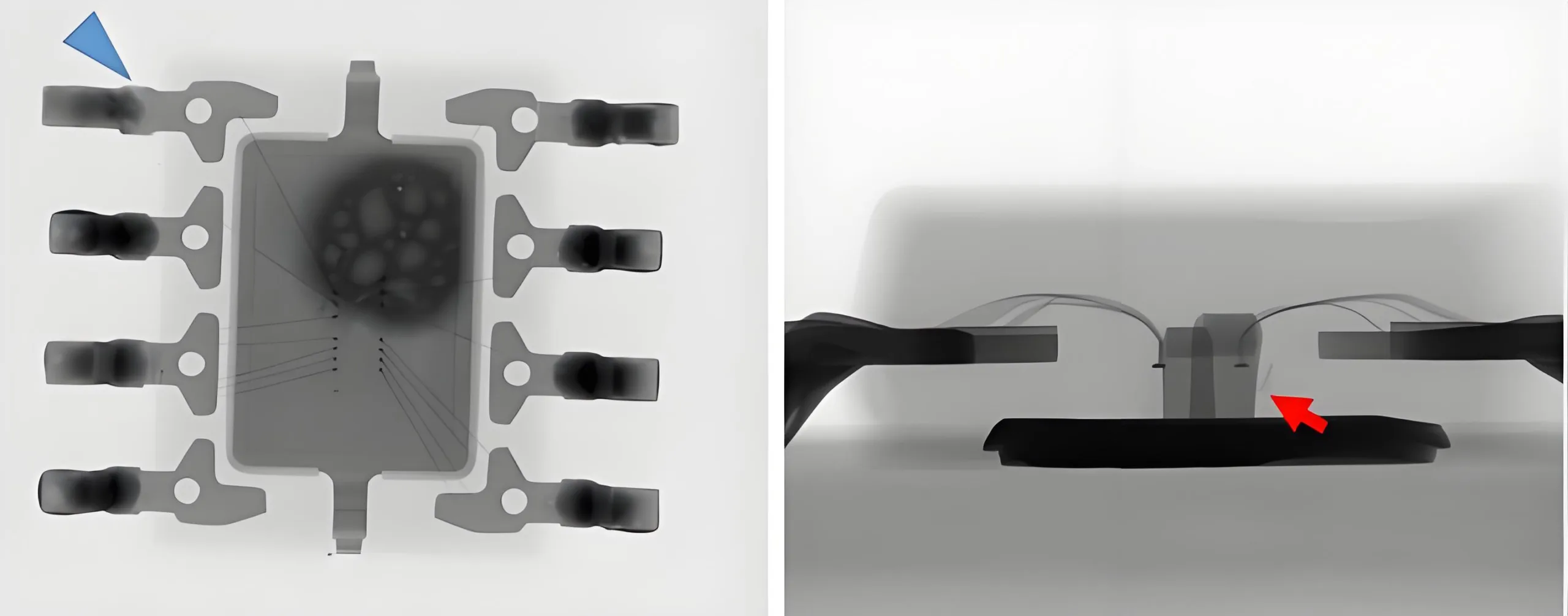

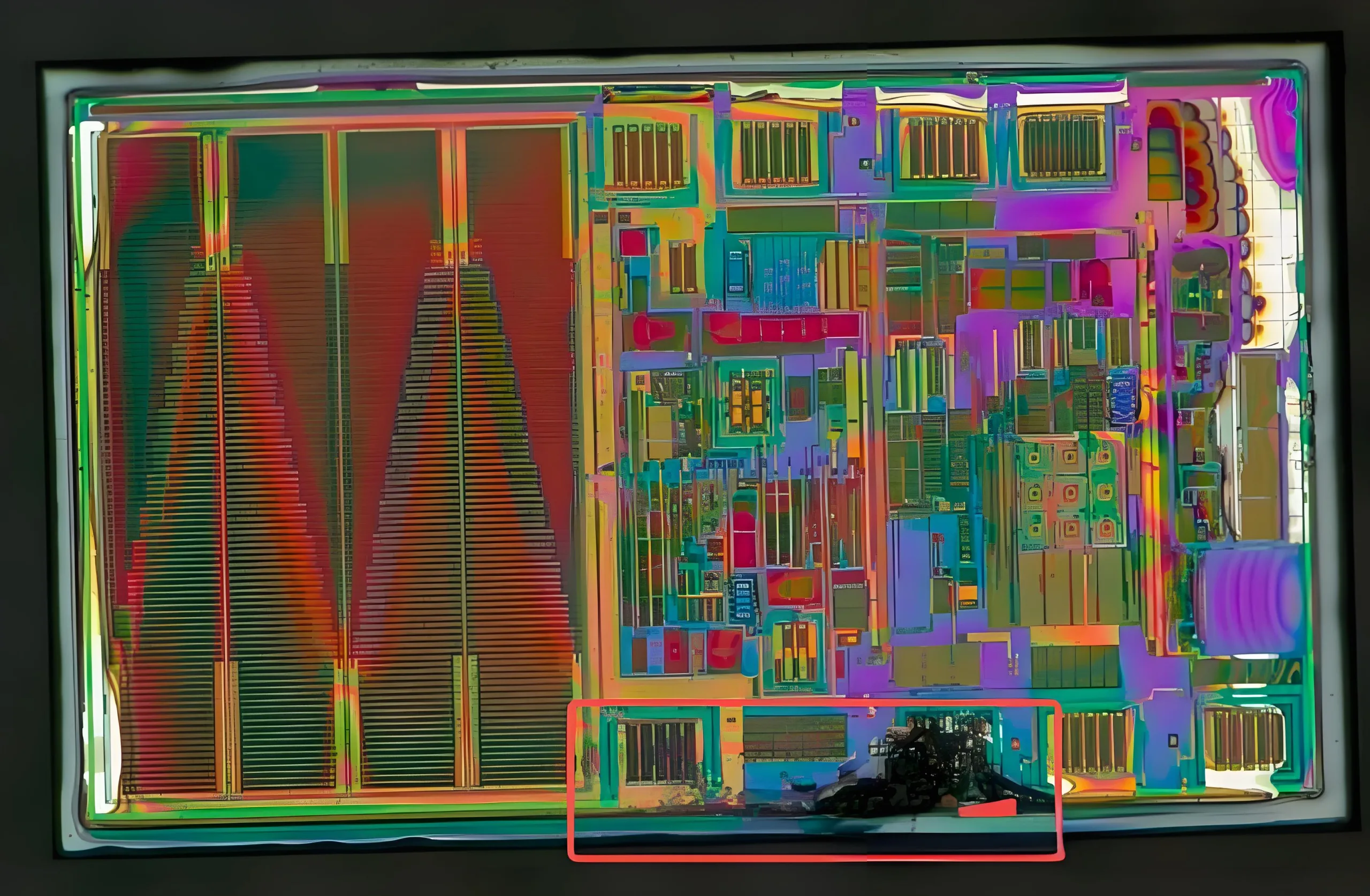

외관이나 음향 스캐닝에서 뚜렷한 이상은 관찰되지 않았습니다., 하지만 엑스레이를 보니 화상 손상이 의심되는 것으로 나타났습니다..

불에 탄 것으로 의심됨

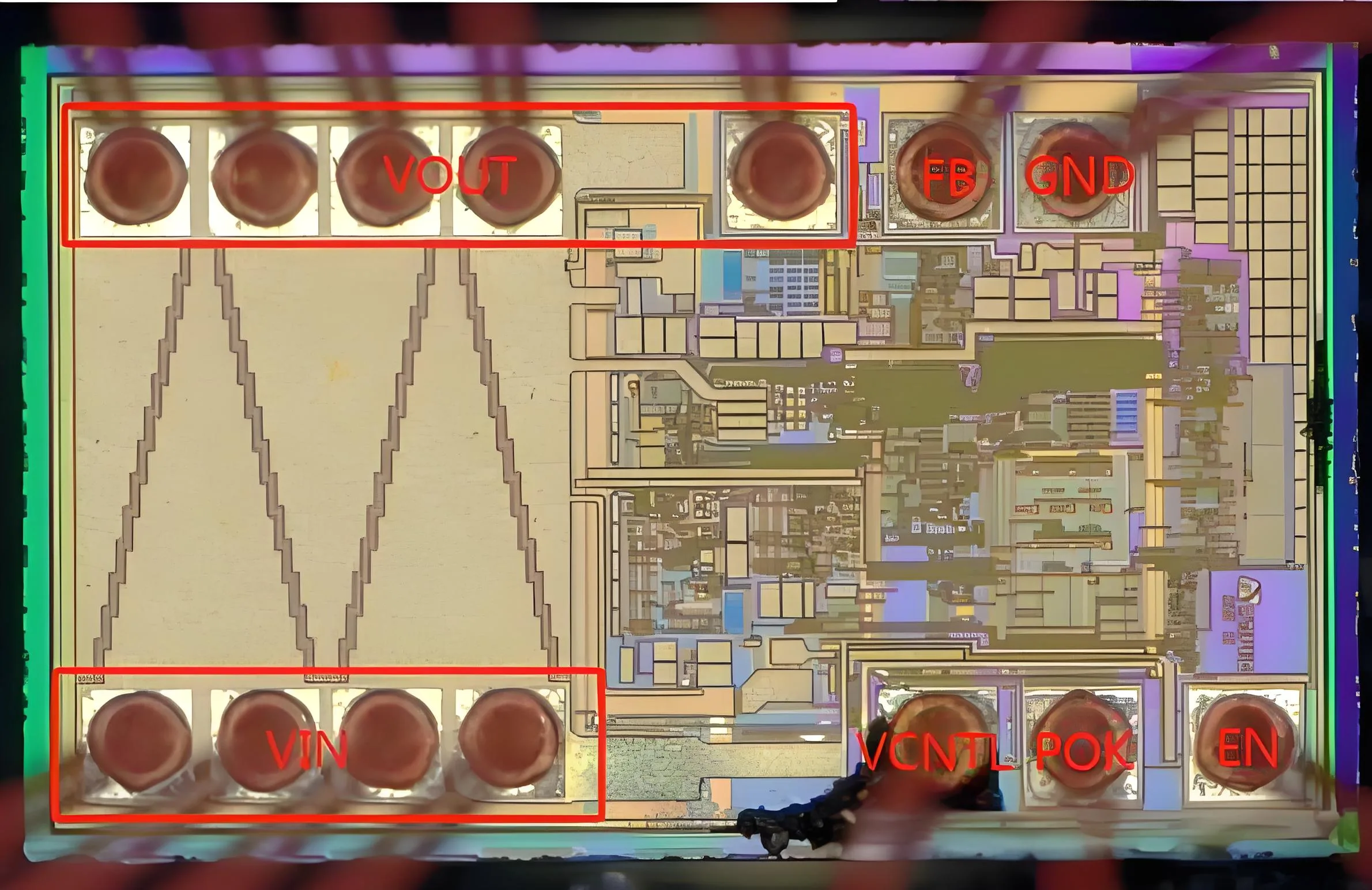

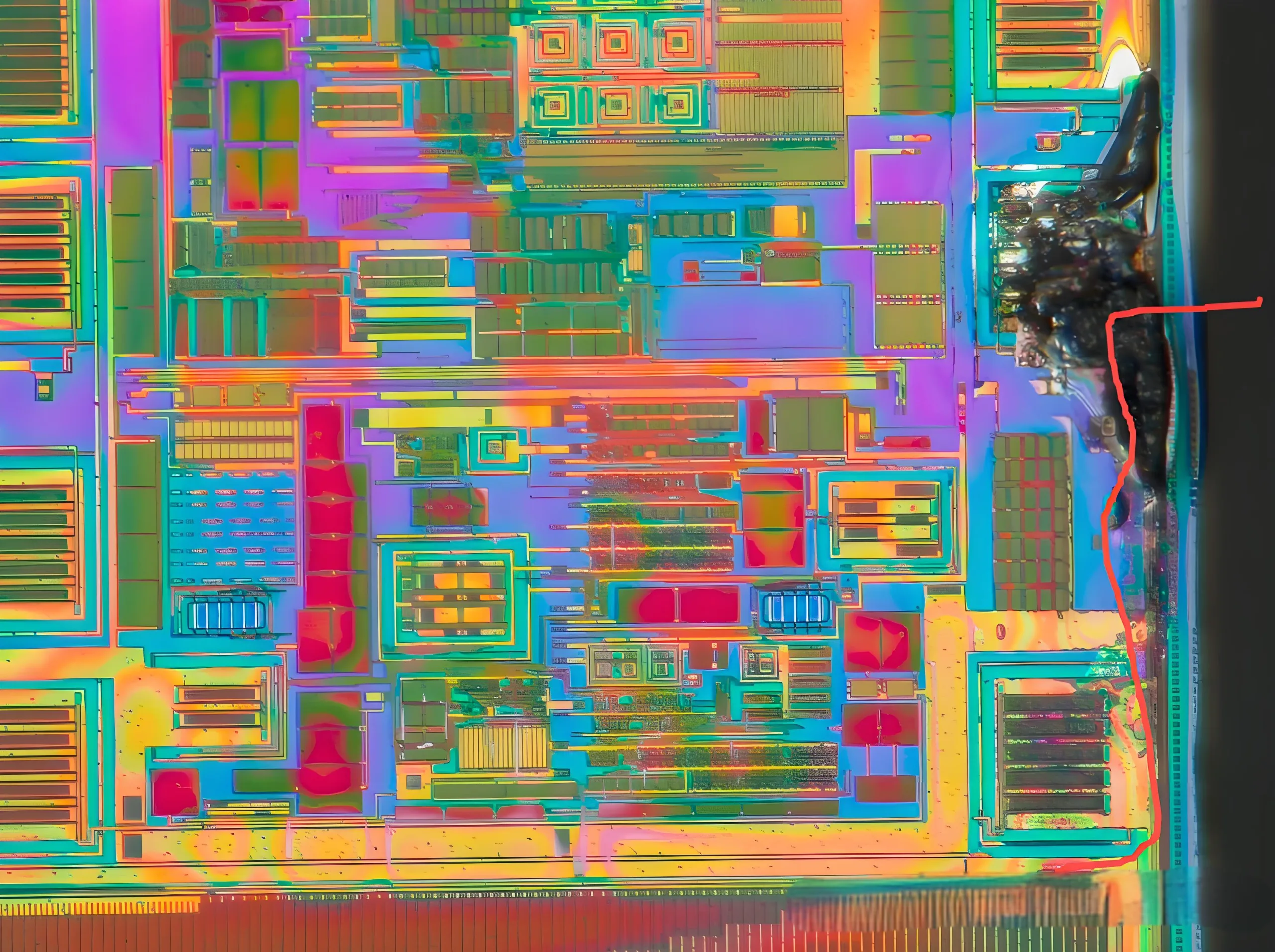

커버를 열면, 칩의 EOS 번아웃은 Vin보다는 VCNTL 핀에서 가장 심각한 것으로 나타났습니다..

칩의 EOS가 소진되었습니다.

칩의 EOS가 소진되었습니다.

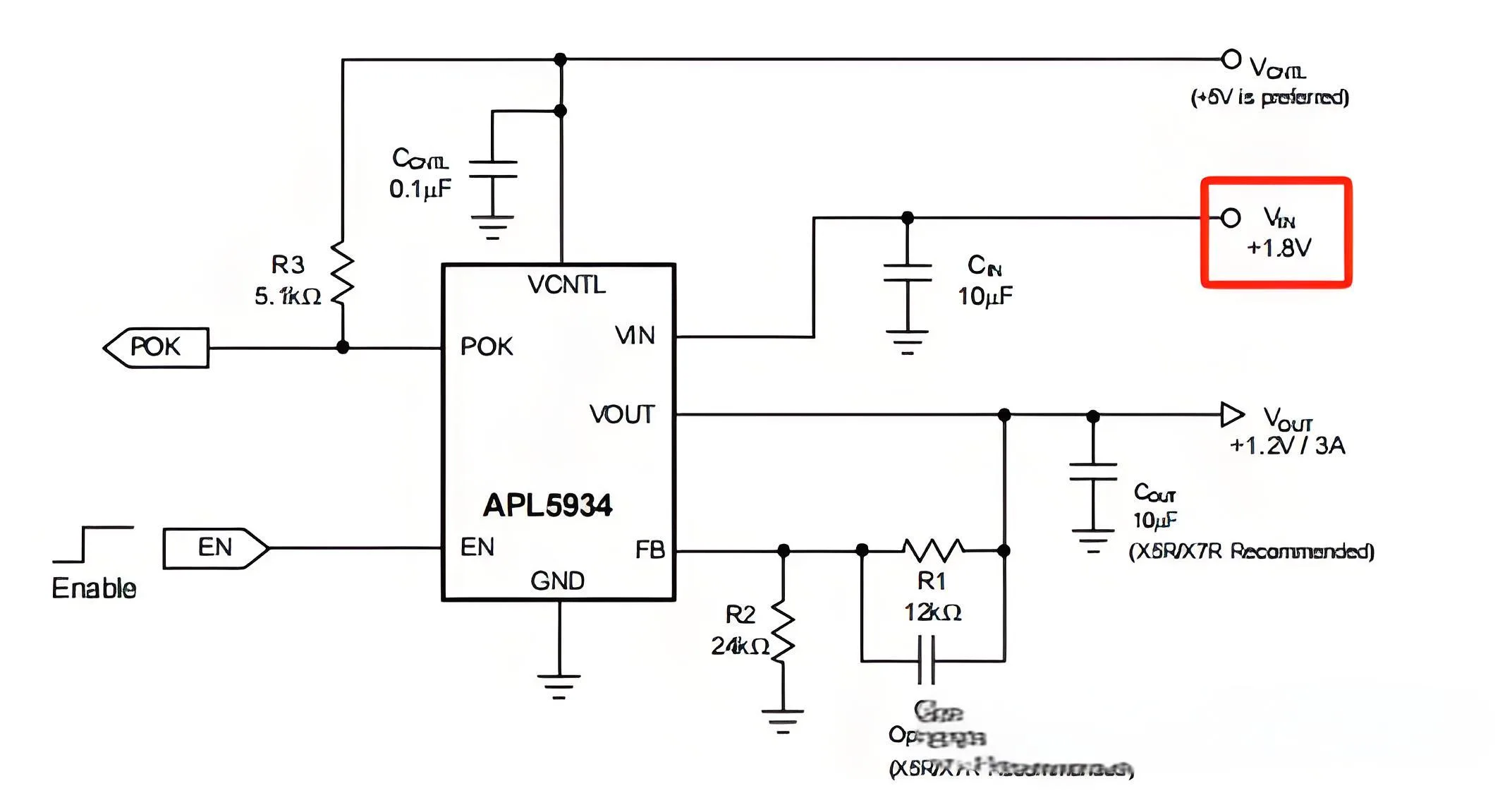

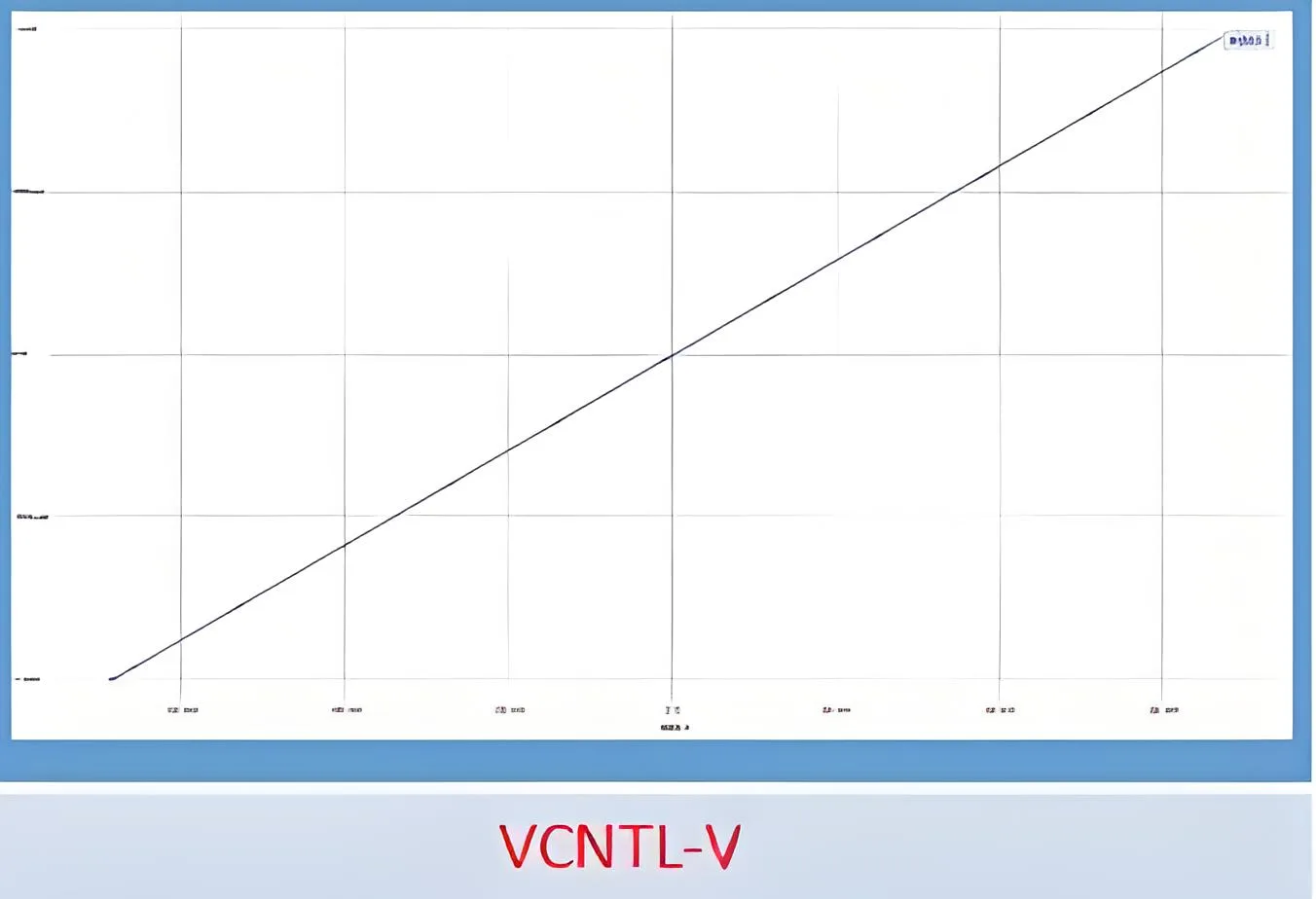

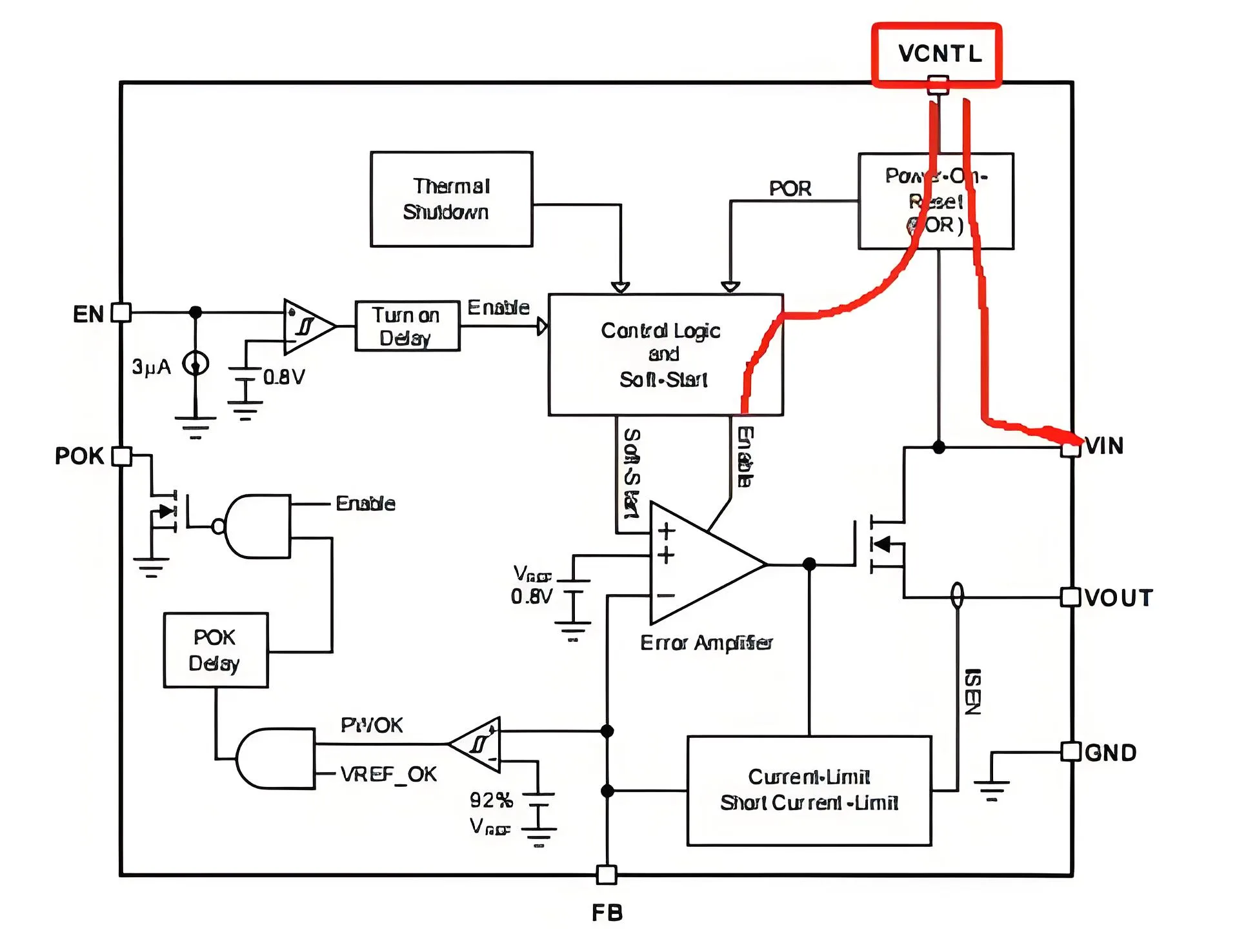

3) 근본 원인 분석: VCNTL에 의해 발생된 과전압 스트레스로 인해 칩 고장이 발생한 것으로 의심됩니다.. VCNTL 핀은 입력 핀으로 정의됩니다., 잠재적으로 과전압 스트레스를 경험할 수 있는.

VCNTL은 과도한 전기적 스트레스를 유발하여 고장을 유발합니다.

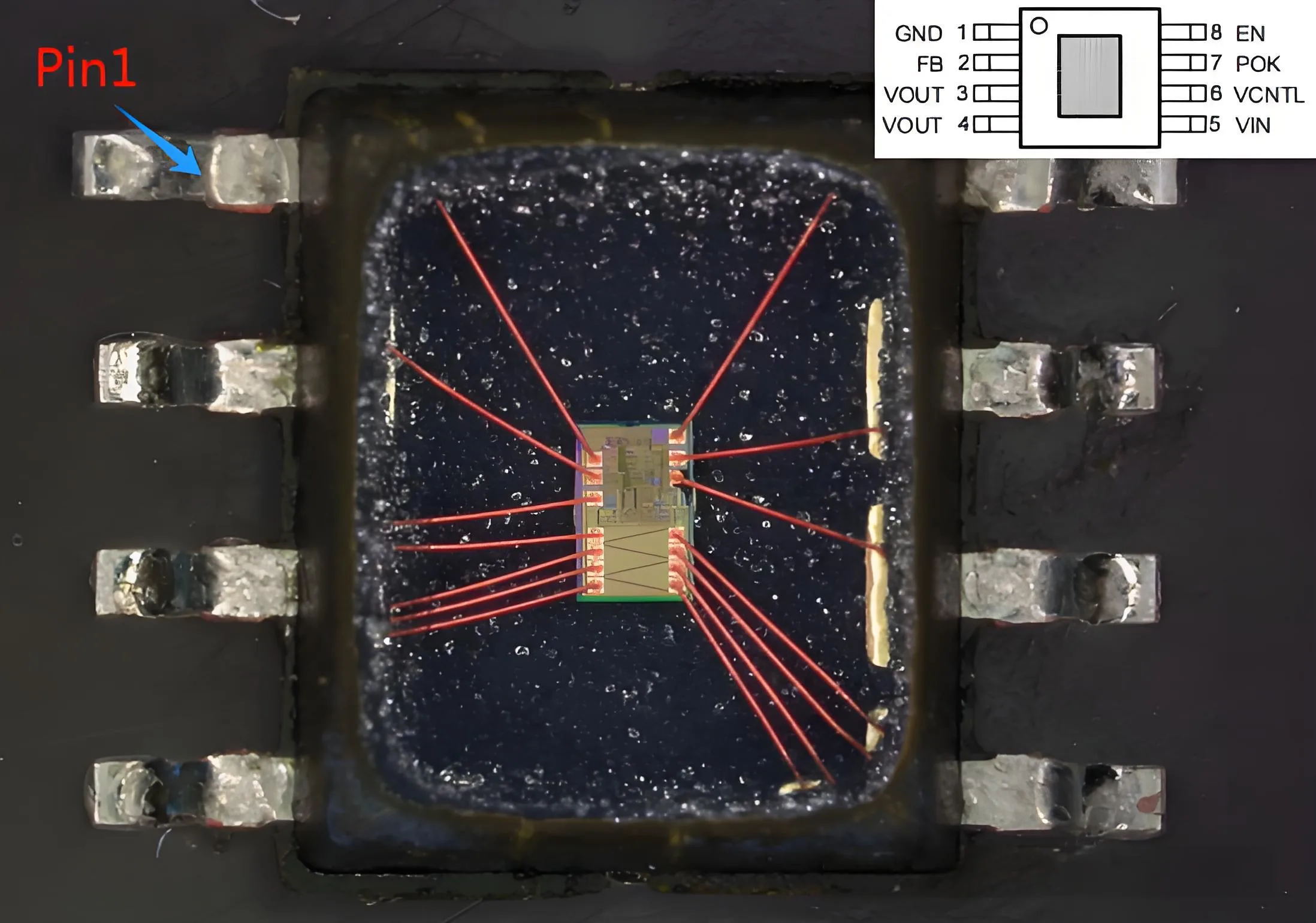

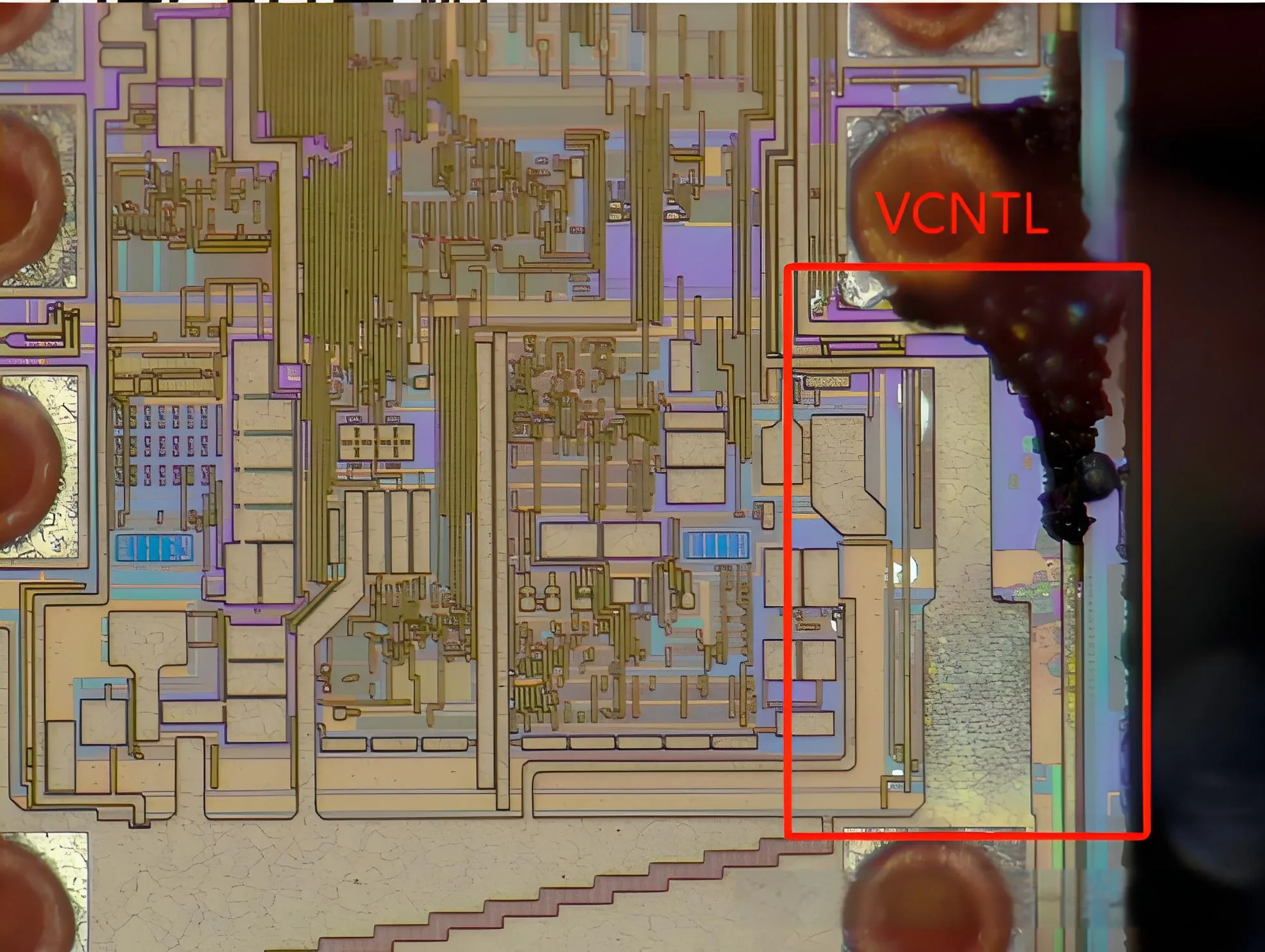

추가 분석에 따르면 VCNTL-VIN 링크를 따라 금속 형태가 녹은 것으로 나타났습니다., VCNTL과 VIN 사이의 IV를 측정하면 단락이 나타났습니다.. 그러므로, VCNTL에 의해 발생한 과전압 스트레스로 인해 칩이 고장났습니다.. 칩의 논리 블록 다이어그램을 분석하여 오류 현상과 논리 기능을 일치시켰습니다..

칩 로직 다이어그램

금속의 최상층을 제거함으로써 칩의 고장이 실제로 VCNTL에 의해 발생된 과전압 스트레스로 인해 발생했음이 밝혀졌습니다..

VCNTL은 과도한 전기적 스트레스를 유발하여 고장을 유발합니다..

VCNTL은 과도한 전기적 스트레스를 유발하여 고장을 유발합니다..

4) 이사회 수준 확인: 분석 후, 보드의 다른 주변 장치 손상으로 인해 VCNTL 핀의 전압 스트레스가 사양 값을 초과한 것으로 확인되었습니다.. 따라서, 이 칩은 “피해자.”

EOS는 장애 분석에서 가장 흔히 발생하는 현상입니다.. EOS 장애 증상을 통해 근본 원인을 식별하는 것은 어려운 일이며 분석가에게는 명확한 논리적 사고와 광범위한 지식이 필요합니다..

UGPCB 로고

UGPCB 로고