Introducere: Războiul la scară milimetrică în designul PCB DDR5

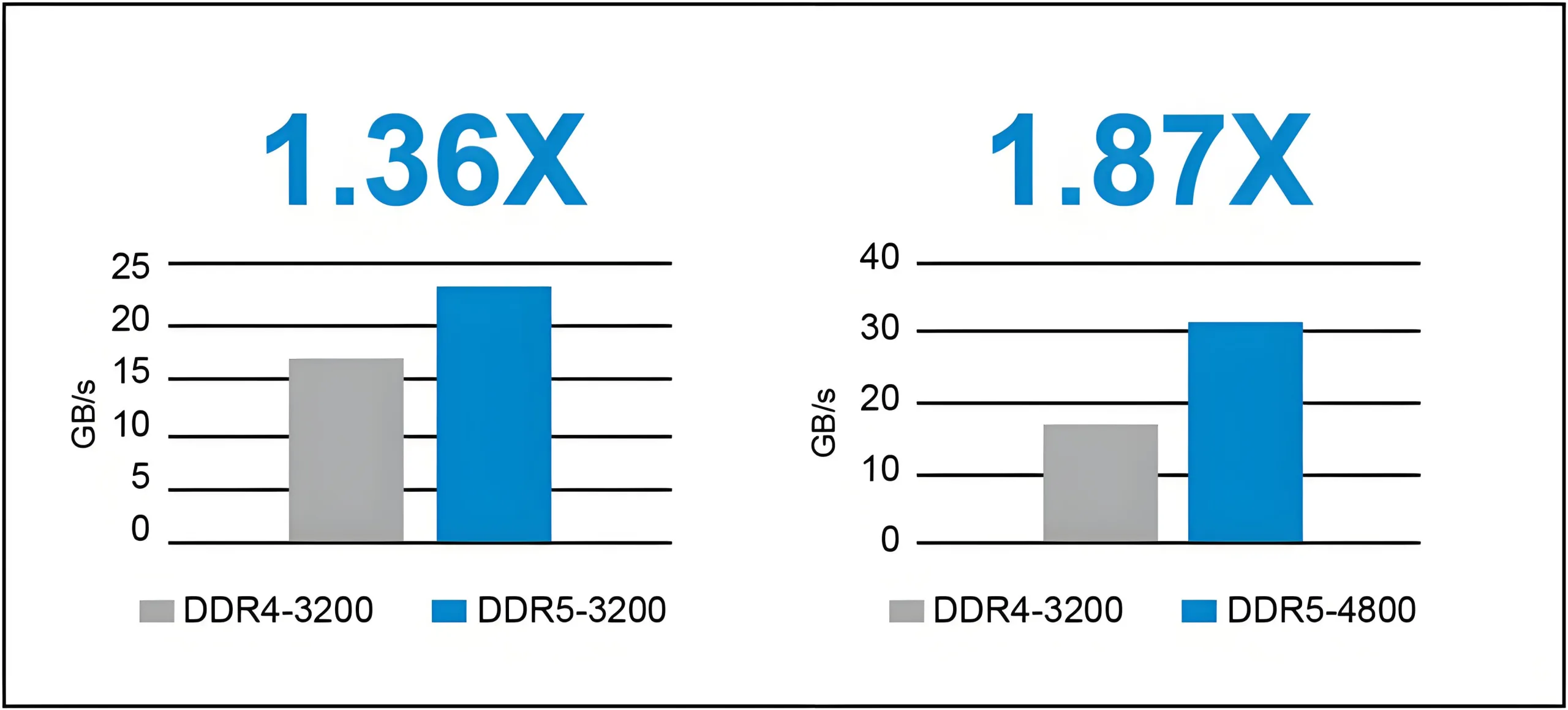

Saltul de la DDR4 la DDR5 marchează o schimbare de paradigmă: ratele semnalului cresc de la 3,200 MT/s la 6,400 MT/s în timp ce tensiunile de funcționare scad la 1,1 V. Această provocare dublă se transformă PCB rutare de la inginerie simplă a conectivității la război de precizie la scară milimetrică. Datele industriei dezvăluie că 80% dintre erorile de proiectare DDR5 provin din probleme de rutare, cu 90% prevenit prin simulare pre-amenajare. Acest articol analizează cinci capcane critice de rutare DDR5, susținută de date empirice și studii de caz, oferind soluții acționabile pentru profesioniștii PCB.

1. Caracteristici fizice DDR5: De ce metodele tradiționale de proiectare PCB eșuează

1.1 Rata semnalului și revoluția lățimii de bandă

Pentru DDR5-6400, frecvența efectivă de ceas atinge 3,200 MHZ, cu rate la fel de rapide ca 0.5 ps (20-80% timpul de ridicare). Acest lucru declanșează:

-

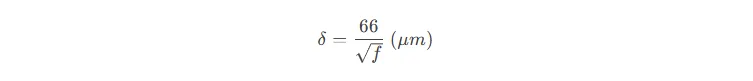

Efect agravat asupra pielii: Curenții de înaltă frecvență se concentrează pe suprafețele conductorilor, reducerea grosimii efective a cuprului la 0.66 μm la 10 GHz.

-

Escaladarea pierderilor dielectrice: substraturi FR4 prezintă o tangentă de pierdere (Df) de 0.02 la 10 GHz, provocând >3 atenuarea semnalului dB/inch.

Validarea formulei (Adâncimea pielii):

La f=10 GHz, δ≈0,66 μm,lăsând cupru tradițional de 1 oz (35 μm) cu <2% utilizare.

2. Cinci câmpuri minate de rutare DDR5 și contramăsuri

2.1 Câmp minat 1: Eroare de sincronizare – Pragul de supraviețuire de ±15 ps

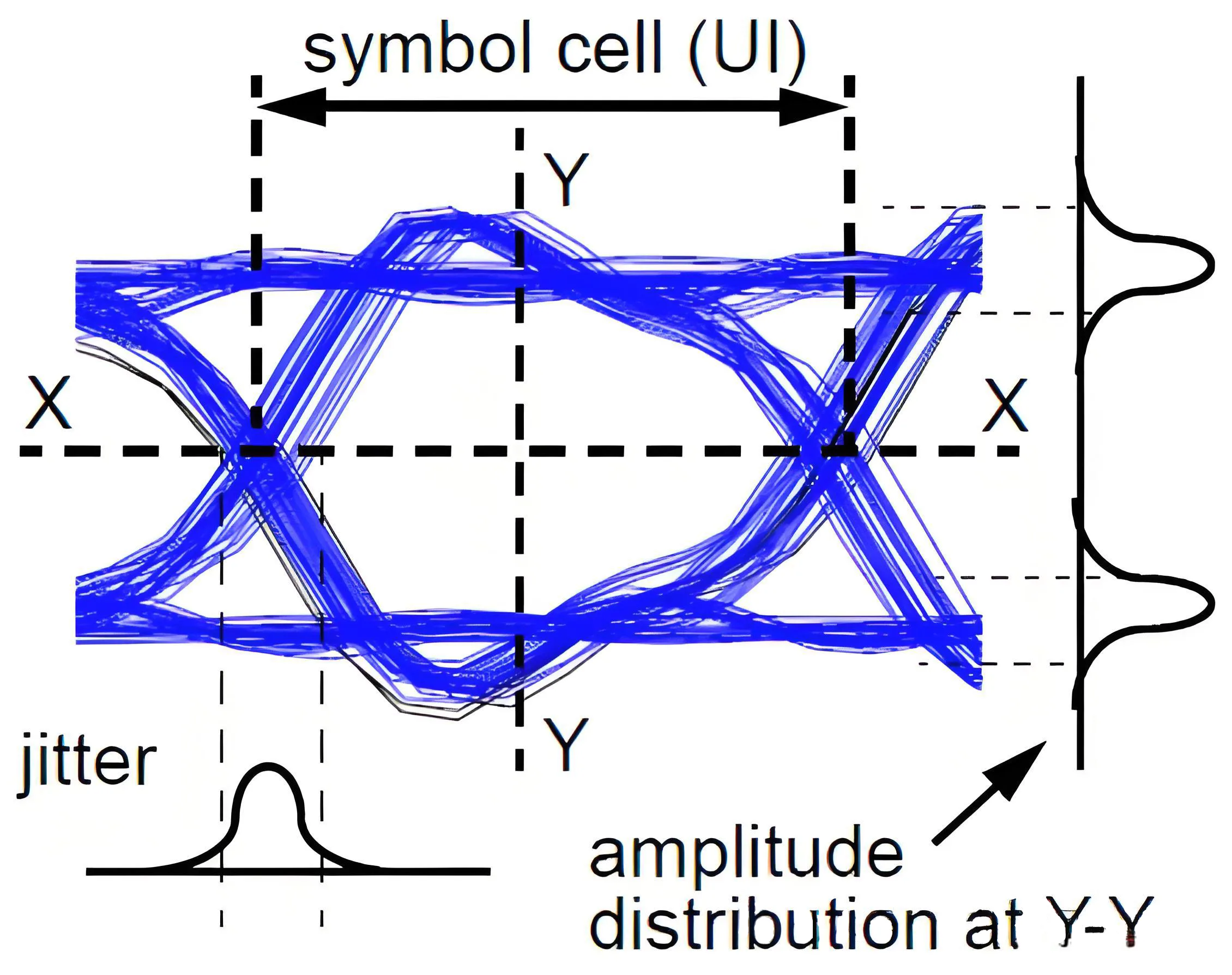

Impact: O nepotrivire de lungime de 5 mil introduce o întârziere de ± 12 ps, prăbușirea lățimii ochiului orizontal cu 30%.

Studiu de caz: Un design GPU a suferit o degradare BER 10−12 la 10−7 datorită oblicului DQ/DQS de 8 mil.

Soluții:

-

3D Compensarea traseului: Înlocuiți meandrele de 90° cu serpentine de 45°, reducerea capacității parazitare prin 30%.

-

Calibrare dinamică a timpului: Efectuați simulări Monte Carlo (Cadence Sigrity) acoperind ±10% variatii de proces.

Formula (Marja de sincronizare):

Tmarginea=Tciclu-(Tco+Tzbor+Tfrământare)

Pentru DDR5-6400 (Tciclu=0,3125 ), alertele de sistem se declanșează când Tmarginea<50 ps.

2.2 Câmp minat 2: Discontinuitate de impedanță – Tsunami de semnal de 5Ω

Risc: Prin cauze de nepotrivire a impedanței >15 Pierdere de întoarcere dB, prăbușirea înălțimii ochiului vertical de 40%.

Date: Fiecare neoptimizat prin adaosuri 0.2 Pierdere de inserție dB la 5 GHz.

Soluții:

-

Prin Revoluție: Implementați vias orb cu laser (≤4mil) cu compensare antipad, limitând variația impedanței la ±3Ω.

-

Optimizare Pad: Folosiți tampoane eliptice (1.5:1 raportul de aspect) pentru a reduce efectele capacitive prin 20%.

Formula (Prin modelul de impedanță):

Zvia≈87ϵr⋅ln(5.98h/(0.8d1+d2))

Unde : grosimea dielectrică, d1: prin diametru, : diametrul tamponului.

2.3 Câmp minat 3: Întârziere încrucișată – Efectul fluture de 0,1 ps/mm

Efect de țesătură de fibre: Variația constantei dielectrice (Δϵr=0,3) din cauza periodicitatii fibrei de sticla 0.6 ps/inch delay skew.

Soluții:

-

Alinierea axei Z: Dirijați semnalele grupului de octeți la unghiuri de ±45° pentru a anula anizotropia dielectrică.

-

Compensare încrucișată: Preîncărcați datele substratului Dk/Df în instrumentele EDA pentru corectarea automată a întârzierilor.

2.4 Câmp minat 4: Power Ripple – Reacția nucleară în lanț de 1 mV

Sensibilitate: 50Ondularea mV la o sursă de 1,1 V crește fluctuația driverului cu 20%.

Simulare: Impedanța țintă PDN trebuie să fie ≤2 mΩ@100 MHz – de 5 ori mai strictă decât modelele tradiționale.

Soluții:

-

3D Matricea condensatorului: Implementați 0,1μF (0402) + 10nF (0201) condensatoare lângă circuite integrate, acoperire 10 kHz–2 GHz.

-

Stâlpi Micro-Cupru: Încorporați stâlpi cu diametrul de 200 μm sub BGA, tăierea inductanței buclei de 30%.

2.5 Câmp minat 5: Întreruperea căii de întoarcere – Bomba EMI invizibilă

Risc EMI: Planurile de referință sparte generează zgomot de mod comun, depășirea limitelor EMI cu 10 DB.

Soluții:

-

Cusătură la sol: Așezați căi de pământ (≤0,1Ω) fiecare 100 mil între straturile de semnal.

-

Legătura cu plan divizat: Folosiți condensatori îngropați (De ex., AVX 0402B) pentru cuplarea de 10nF între diviziunile de putere.

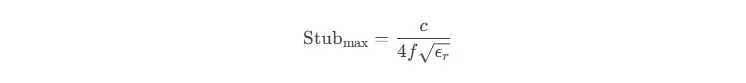

3. Reguli de aur pentru design DDR5: Formule și lanțuri de instrumente

3.1 Prin limitarea stub:Pentru DDR5-6400 (f=3,2 GHz) pe FR4: Ciotmax≤14,7 mm.

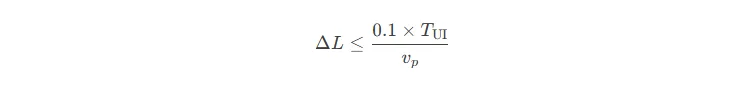

3.2 Toleranță diferențială de pereche:

Cu TUI= 0,3125 ns şi vp=6 inch/: ΔL≤1,9 mil.

3.3 Țintă de impedanță PDN:

Pentru ondulație de 50 mV și curent tranzitoriu de 10 A: Z.ţintă≤5 mΩ.

4. Reinginerirea procesului de proiectare PCB: De la încercare și eroare la bazată pe simulare

4.1 Planificarea topologiei:

-

Model vias în HFSS; optimizați dimensiunile antipad.

-

Extrageți impedanța de stivuire prin SIwave; construiți biblioteci de parametri S.

4.2 Execuție de rutare:

-

Activați verificări de impedanță în timp real în Allegro; încălcări ale semnalizării automate.

-

Implementați topologia fly-by cu ≤2 mil înclinație intra-grup.

4.3 Validare:

-

Efectuați teste cu diagrama ochilor (Anunţuri Keysight) cu înălțimea ochilor ≥70 mV.

-

Măsurați curbele TDR; limita variația impedanței la ±5%.

Concluzie: The “Trei Corpuri” Legea designului DDR5

Sub viteza de GHz, milivolt-zgomot, și constrângeri de toleranță la microni, Designul PCB DDR5 intră în a “mecanica cuantică” eră. Victoria în războiul de integritate a semnalului necesită convergența științei materialelor (Substraturi cu Dk scăzut), procese avansate (mSAP), și stăpânirea simulării.

LOGO UGPCB

LOGO UGPCB