Im Bereich Elektrotechnik, die Schichtanzahl von a Leiterplatte (Leiterplatte) ist oft ein direkter Indikator für die Komplexität und technologische Ausgereiftheit eines Produkts. Während die meisten Ingenieure routinemäßig damit arbeiten 2, 4, oder 6-Lagen-Platinen – in der Unterhaltungselektronik kommen sogar kostenoptimierte Lösungen wie zum Einsatz “Pseudo-8-Schicht” Bretter (6 funktionelle elektrische Schichten plus 2 Isolierschichten für Dicke)– Die Landschaft verändert sich dramatisch bei High-End-Servern, Hochleistungs-Computer-Motherboards, und modernste Kommunikationsausrüstung. Hier, Leiterplatten mit 16, 32, oder auch 64 Schichten sind üblich. Dies wirft eine kritische Frage auf: Was sind die zugrunde liegenden Designprinzipien und Fertigungstechnologien, die dies ermöglichen? Leiterplatten mit hoher Schichtanzahl? Dieser Artikel bietet eine ausführliche Analyse der technischen Aspekte, Kernherausforderungen, und fortschrittliche Fertigungslösungen für Leiterplatten mit hoher Schichtanzahl.

Warum Leiterplatten mit hoher Schichtanzahl?? Mehr als nur ein Routing-Spiel

Bei der Erhöhung der Anzahl der PCB-Lagen geht es nicht darum, beeindruckende Zahlen anzustreben. Der grundlegende Treiber ist der exponentielle Anstieg der Leistungsanforderungen moderner elektronischer Geräte. Wenn die Chip-Pin-Dichte weiter ansteigt (z.B., BGA-Pakete mit über 2500 Lötkugeln), Signalgeschwindigkeiten erreichen den GHz-Bereich (z.B., PCIE 5.0 bei 32 GT/s), und Systeme müssen gleichzeitig mit Hochgeschwindigkeits-Digital umgehen können, HF-Analog, und Hochleistungssignale, traditionell 4 oder 6-Schicht-Platten werden unzureichend.

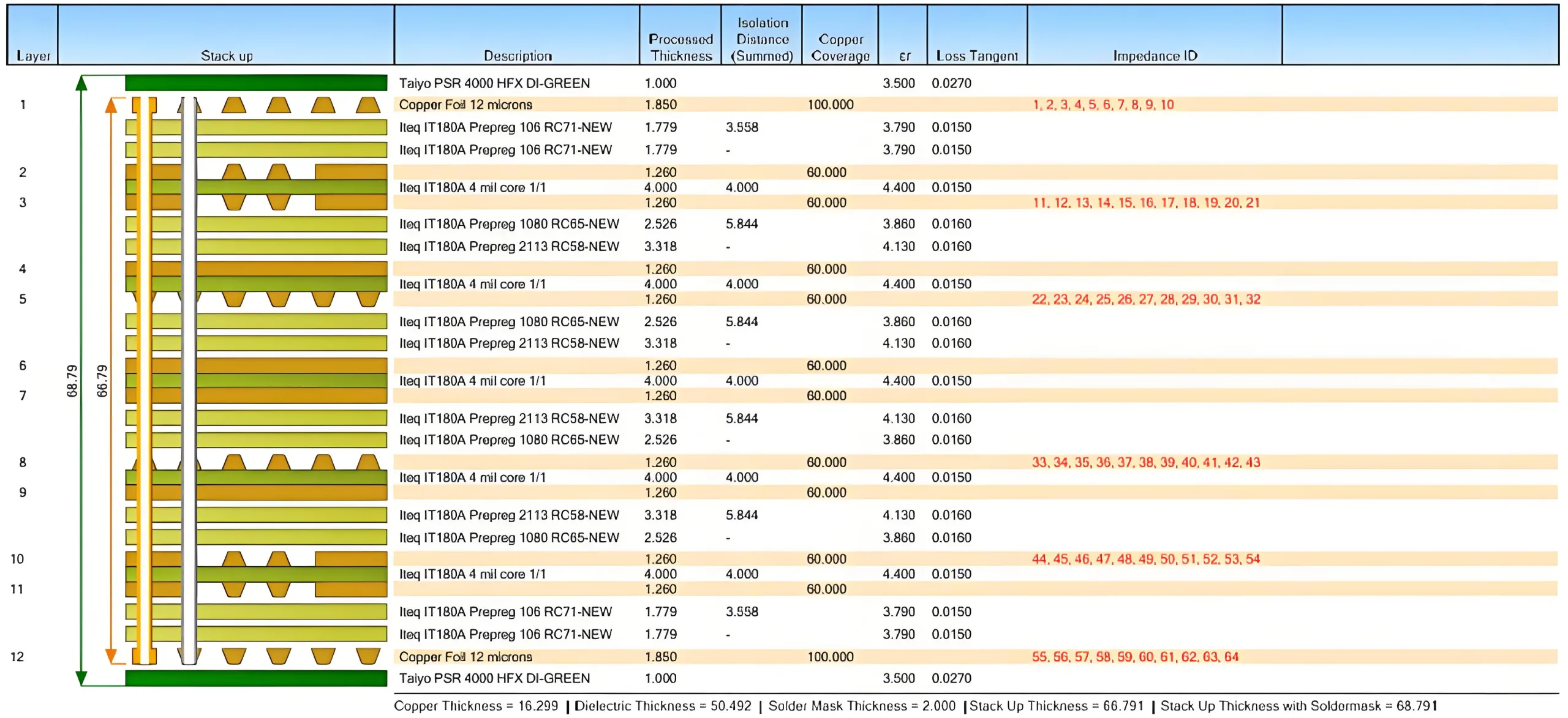

Der Kernwert von Leiterplatten mit hoher Lagenzahl liegt in der Bereitstellung ausreichender Routing-Ressourcen und vollständiger Referenzebenen. Ein typischer 12-Lagen-Plattenaufbau könnte sein: Signal 1 / Boden / Signal 2 / Leistung 1 / Signal 3 / Boden / Signal 4 / Leistung 2 / Signal 5 / Boden / Signal 6. Das ist symmetrisch “Masse-Signal-Strom-Signal-Masse” Stapeln (Einhaltung von Richtlinien wie IPC-2141A) Kontrolliert effektiv die Impedanz und bietet einen rauscharmen Rückweg für Hochgeschwindigkeitssignale. Statistiken zeigen, dass dies bei Geräten wie Rechenzentrums-Switches der Fall ist, Designs mit PCBs mit 20+ Schichten können das Übersprechen in kritischen Netzwerksignalen um mehr als ein Vielfaches reduzieren 60% (Daten aus dem IPC TR-579-Bericht).

Designherausforderungen für Leiterplatten mit hoher Schichtanzahl: Darüber hinaus “Spuren zeichnen”

Signalintegrität und Impedanzkontrolle

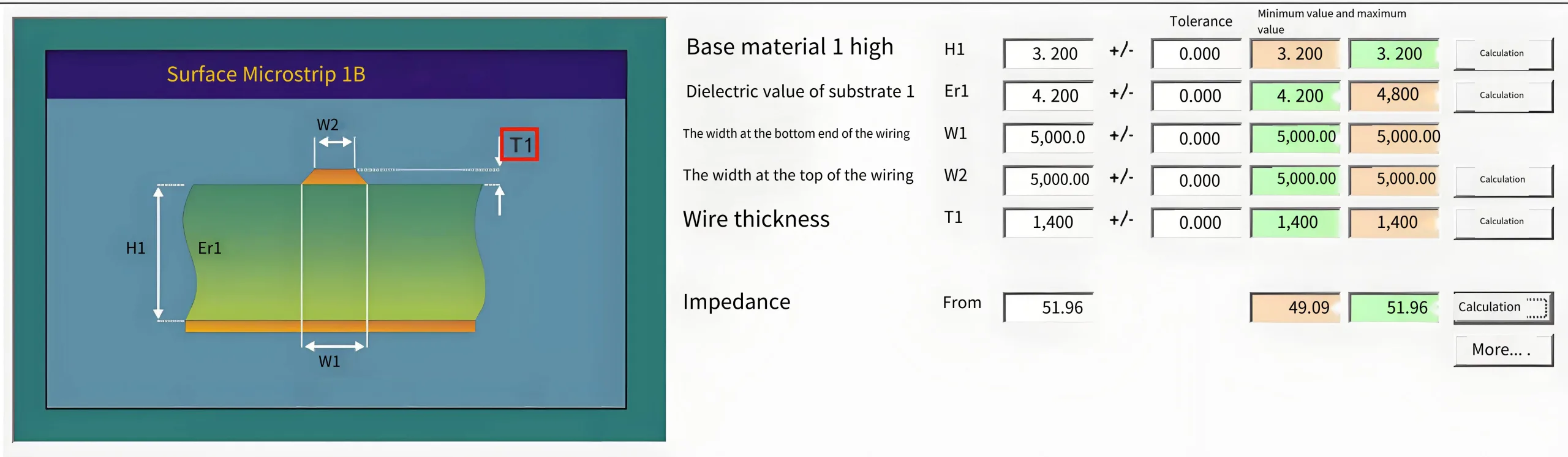

In High-Speed-Ausführung, PCB-Leiterbahnen sind keine einfachen elektrischen Verbindungen mehr, sondern müssen präzise gesteuerte Übertragungsleitungen sein. Abweichungen in der charakteristischen Impedanz (z.B., 50Ω Single-Ended, 90Ω/100Ω Differenz) direkt zu einer Signalreflexion führen, Überschießen, und Schließen des Datenaugendiagramms. Die Impedanz hängt hauptsächlich von der Leiterbahnbreite ab (W), dielektrische Dicke (H), Dielektrizitätskonstante (εr), und Kupferdicke. Industriestandard-Tools wie Polar Si9000 modellieren dies mithilfe vereinfachter Formeln (für Mikrostreifenleitungen):

Z0 ≈ (87 / √(εr + 1.41)) * ln(5.98 * H / (0.8 * W + T))

wobei T die Spurdicke ist. Für gängiges FR-4-Material (εr ≈ 4.2 @ 1GHz), um eine Impedanz von 50 Ω mit einer dielektrischen Dicke von H = 5 mil zu erreichen, Die Leiterbahnbreite W muss auf etwa 100 mm eingestellt werden 8.5 Mil. Jedoch, Ungleichmäßigkeit in der laminierten Struktur von Platten mit hoher Schichtdicke, der Glaswebeffekt, und Produktionsätztoleranzen (typischerweise ±10 %) Alle führen zu Impedanzschwankungen. Der IPC-6012D-Standard erlaubt bei Boards mit kontrollierter Impedanz eine Abweichung des Messwerts von der Nennimpedanz um ±10 %, aber High-End-Anwendungen erfordern jetzt Toleranzen von nur ±7 %.

Leistungsintegrität und PCB-Wärmemanagement

Mit zunehmender Schichtanzahl, die Komplexität des Stromverteilungsnetzes (PDN) Design wächst exponentiell. Die Kernspannungen können bis zu 0,8 V betragen, wobei die Übergangsströme Hunderte von Ampere erreichen können. In diesem Szenario, Die Zielimpedanz der Leistungsebenen muss extrem niedrig sein (z.B., <1 Mω) Spannungswelligkeit zu unterdrücken. Dies erfordert eine sorgfältige Planung der Platzierung des Entkopplungskondensators, Optimierung der Zwischenebenenkapazität zwischen Leistungs- und Masseebene (berechnet von C = ε0 * εr * A / d, Dabei ist A die Überlappungsfläche und d die Dielektrikumsdicke), und erfordern möglicherweise dedizierte Leistungsschichten. Außerdem, erhöhte Leistungsdichte durch High-Density-Routing (übersteigend 100 W/cm² in einigen ASIC-Bereichen) erfordert eine verbesserte Kühlung durch thermische Via-Arrays, eingebettete Kupfermünzen, oder Metallsubstrate, Dadurch wird die Stapelkonstruktion und -verarbeitung noch komplexer.

Die Alchemie der Leiterplattenherstellung: Die Präzisionsprozesskette für High-Layer-Boards

Die Umsetzung des Designs in die physische Realität stellt eine weitere große Herausforderung für Leiterplatten mit hoher Lagenanzahl dar. Der Kernprozess kann als präziser Zyklus von zusammengefasst werden “Laminieren – Ausrichten – Bohren – Plattieren.”

Schicht-zu-Schicht-Ausrichtung: Die Kunst der Registrierung auf Mikrometerebene

Alle Schichten einer Mehrschichtplatte (Innenschichtkerne und Prepreg) müssen unter hoher Temperatur und hohem Druck zu einer Einheit laminiert werden. Eine Fehlausrichtung der Schichten kann dazu führen, dass Bohrer Leiterbahnen abschneiden, Erstellen Sie Shorts, oder Impedanzdiskontinuitäten verursachen. Für eine 16-Lagen-Platte, wenn der mittlere Ausrichtungsfehler pro Schicht beträgt 25 μm (die von der IPC-A-600G-Klasse zugelassene grafische Registrierungstoleranz 3), Der kumulative Fehler im schlimmsten Fall könnte größer sein 100 μm – genug, um a zu gefährden 0.2 mm BGA-Pad.

Führende Hersteller wie UGPCB bewältigen diese Herausforderung mit Laser Direct Imaging (LDI) Und hochpräzise optische Ausrichtungssysteme. Ausrichtungsstifte Und globale Referenzskalen auf jeder Kernschicht geätzt, kombiniert mit CCD-Bilderfassung und Servoeinstellung, kann die Registrierung von Schicht zu Schicht steuern 15 μm (Daten basierend auf Prozess-Whitepapers führender Branchenanbieter). Zusätzlich, Materialrheologieanalyse Die Vorhersage des Harzflusses und der Glasfaserausrichtung des Prepregs während der Laminierung ermöglicht eine Vorkompensation der Dimensionsverformung, Gewährleistung einer gleichmäßigen dielektrischen Dicke nach dem Pressen.

Über die Verbindung: Von Durchgangslöchern bis hin zu HDI mit beliebiger Schicht

Herkömmliche Durchgangslöcher durchdringen die gesamte Plattendicke, Sie beanspruchen erheblichen Routing-Platz in Leiterplatten mit hoher Lagenzahl und verursachen Probleme mit langen Signalrückwegen. daher, Hochdichte Interconnect (HDI) Technologie ermöglicht flexiblere Ebenenübergänge Blind Vias (von der Oberfläche bis zur inneren Schicht), vergrabene Durchkontaktierungen (Innenschicht zu Innenschicht), Und Mikrodurchkontaktierungen (Durchmesser ≤ 0.15 mm).

Zum Beispiel, A “1+N+1” HDI-Struktur (wobei die Oberflächenschichten Mikrovias verwenden und die Mitte ein traditioneller N-Schicht-Kern ist) kann die Routing-Dichte um ein Vielfaches erhöhen 40% ohne die Gesamtzahl der Schichten zu erhöhen (unter Bezugnahme auf den HDI-Designstandard IPC-2226). Jedoch, Dies führt zu Prozesskomplexitäten wie Sequentielles Laminierbohren, durch Füllen und Plattieren, Und mehrere Laminierzyklen. Hersteller müssen ausrüsten Laserbohrmaschinen (für Microvias), vertikale Vakuumstopfmaschinen (um eine lunkerfreie Befüllung zu gewährleisten), Und Plasma-Reinigungsgeräte (um Bohrschlamm zu entfernen), und strenge Leistungen erbringen Flying-Probe-Tests Und Vierleiter-Kelvin-Test um die Zuverlässigkeit jedes Kopplungspunkts zu überprüfen.

Zukünftige Trends: Materialinnovation und simulationsgesteuerte Design-Fertigungs-Integration

Die Entwicklung von Leiterplatten mit hoher Schichtanzahl geht weiter. Da die Signalraten mithilfe der PAM4-Modulation auf 56 Gbit/s und darüber hinaus ansteigen, verlustarme Materialien (wie Panasonic MEGTRON 6, Rogers RO4000-Serie) mit εr so niedrig wie 3.2 und Dissipationsfaktoren (Df) unten 0.002 werden übernommen. Gleichzeitig, eingebettete Komponenten (wie vergrabene Widerstände und Kondensatoren) Und Integration von Halbleitergehäusen (z.B., Intels EMIB, SoIC von TSMC) verwischen die Grenzen zwischen PCBs und ICs.

Für Designer und Beschaffungsspezialisten, Auswahl eines qualifizierten hohe Schichtzahl PCB-Lieferant ist von größter Bedeutung. Über die Konzentration auf sie hinaus maximale Layerfähigkeit (z.B., stabile Massenproduktion von 32 Schichten), Impedanzkontrolle Fähigkeit (ob sie Impedanztestberichte bereitstellen), Und HDI-Prozessebene (Mindestlochgröße/Spurbreite), Es ist wichtig, sie zu bewerten Designunterstützungsdienste (wie SI/PI-Simulation und Stack-up-Optimierungsberatung) Und Qualitätskontrollsystem (Einhaltung der IPC-Klasse 3 Standards und Verfügbarkeit umfassender Inspektionsgeräte wie AOI, AVI, 3D Röntgenaufnahme).

Ich suche eine hohe Zuverlässigkeit, leistungsstark mehrschichtige Leiterplatte Lösung? Kontaktieren Sie einen professionellen Lieferanten mit umfassenden Fähigkeiten von der Designsimulation bis zur Präzisionsfertigung, um eine zu erhalten Vorschlag für ein individuelles Stack-up-Design Und Sofortangebot für Ihr Projekt ist der erste entscheidende Schritt zum Erfolg. Im Zeitalter des Internet of Everything und der Computerexplosion, Leiterplatten mit hoher Lagenzahl sind nicht mehr nur Träger; Sie sind der Grundstein für die Leistungsgrenzen elektronischer Systeme.

UGPCB-LOGO

UGPCB-LOGO

Ich bin mir nicht sicher, woher Sie Ihre Informationen beziehen, aber tolles Thema. Ich muss etwas Zeit damit verbringen, mehr zu lernen oder mehr zu verstehen. Vielen Dank für die wunderbaren Informationen. Ich habe diese Informationen für meine Mission gesucht.