Einführung

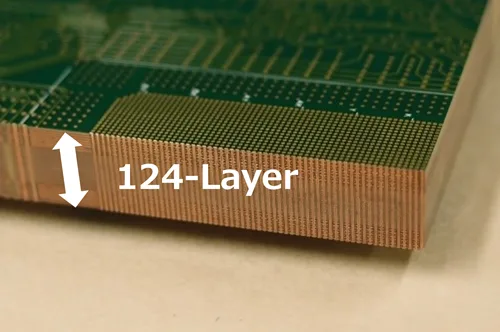

Angetrieben von künstlicher Intelligenz (KI) und Hochleistungs-Computing (HPC), Die globale Elektronikindustrie befindet sich einer technologischen Revolution, auf die konzentriert ist “hohe Dichte, hohe Geschwindigkeit, und hohe Zuverlässigkeit.” Im Mai 2025, ein führender Leiterplattenhersteller enthüllte die weltweit erste kommerzielle 124-Layer-Druckscheidescheibe, Brechen der langjährigen 108-Schicht-Industriesperre und bei der Aufrechterhaltung der Standarddicke von 7,6 mm. Dieser Meilenstein bietet nicht nur kritische Hardware -Unterstützung für KI -Server, Halbleitertests, und Verteidigungssysteme, aber auch neue Grenzen in der elektronischen Verpackungstechnologie freischalten.

Brechen der 108-Schicht-Barriere: Engineering-Lösungen hinter 124-Layer-PCBs

Präzisionsherstellung Innovationen

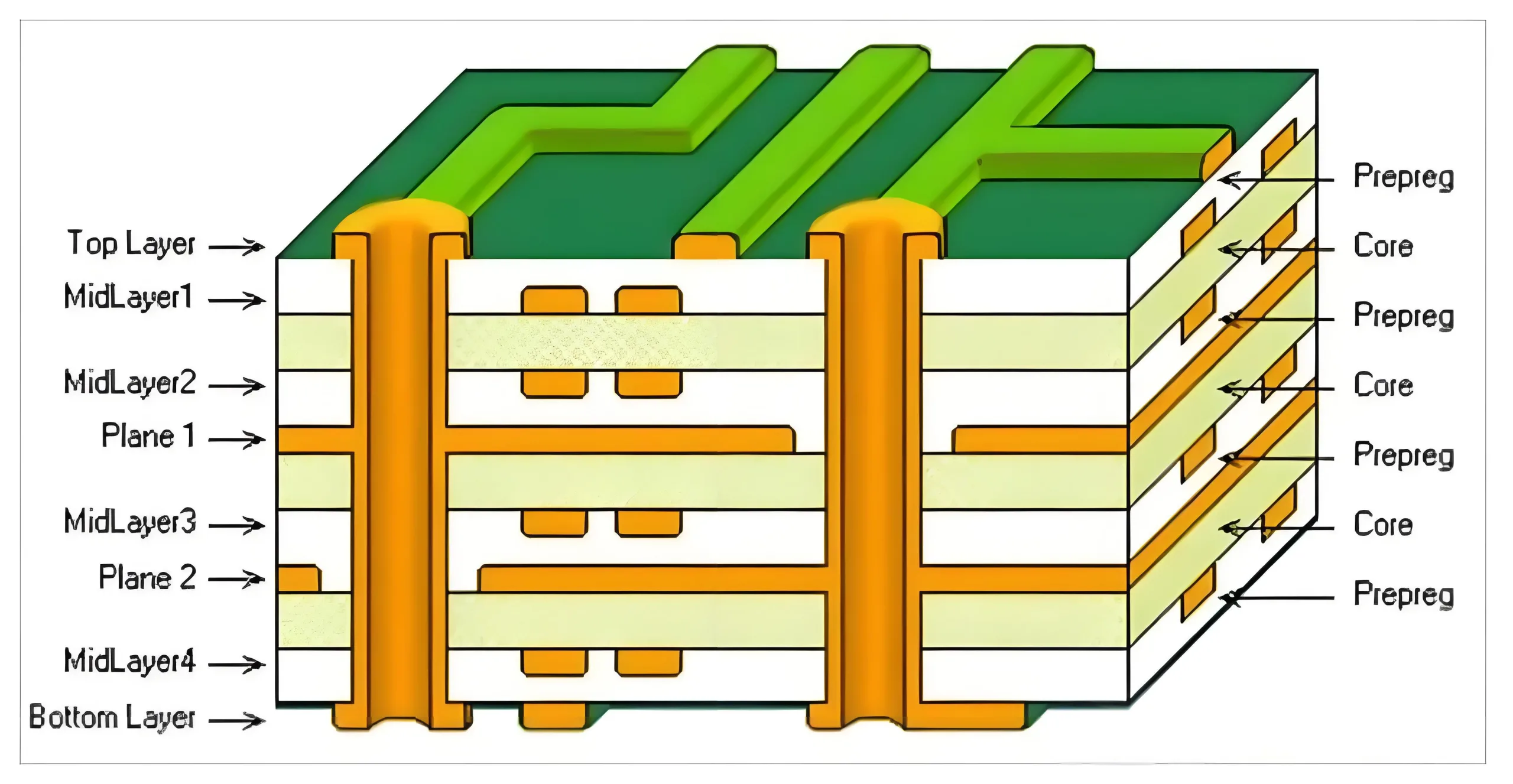

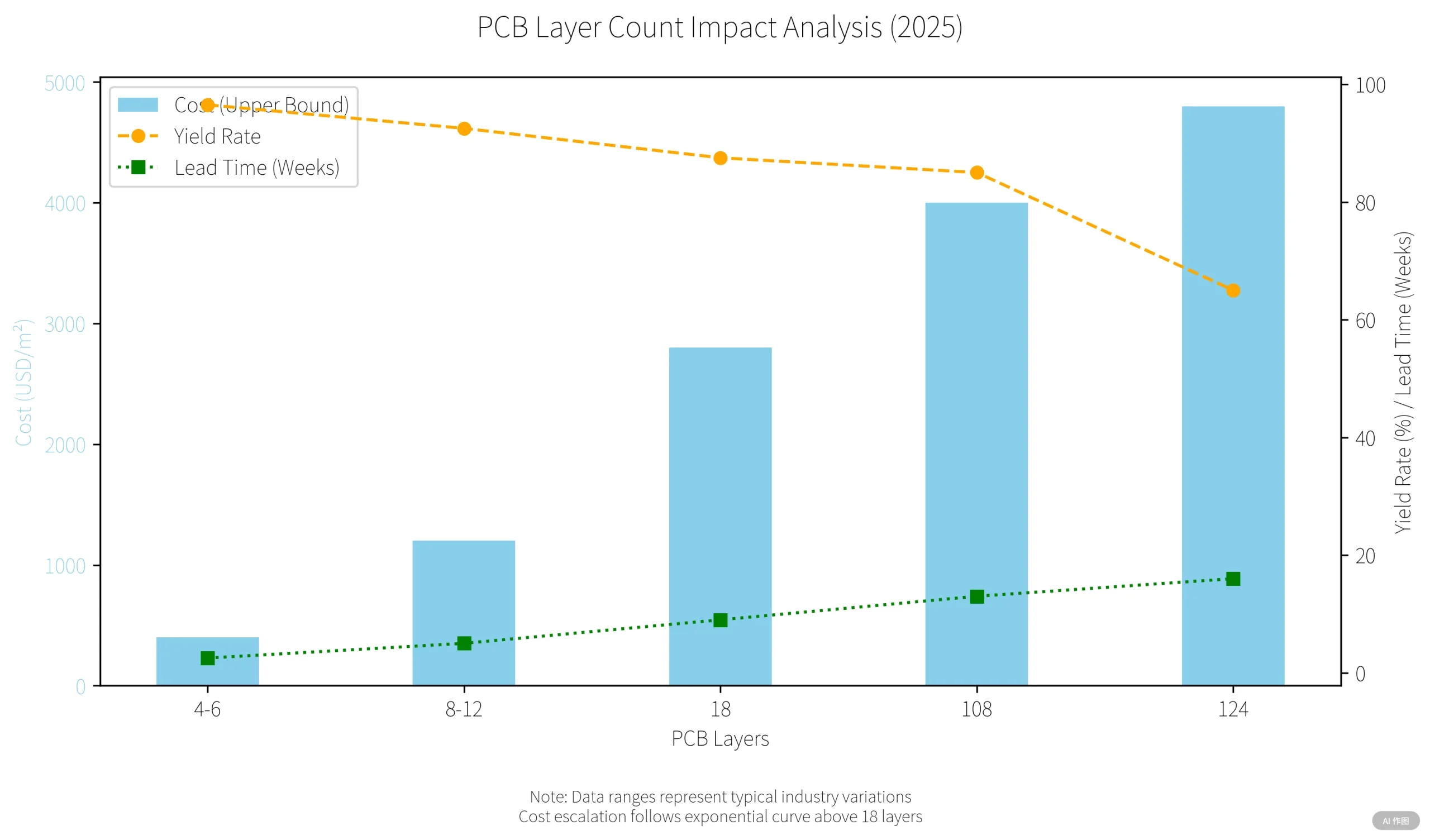

Traditionell PCB -Designs mechanische und thermische Einschränkungen bei Gesicht bei 100 Schichten aufgrund von Inkonsistenzen des Harzflusses, durch Zusammenbruch, und Schichtfehlausrichtung. Der Durchbruch 124-Schicht-PCB erreicht a 15% Schicht erhöht sich durch:

-

Ultradünne Dielektrika: 25µm Schichten unter Verwendung von Material mit niedrigem Verlust (z.B., Fällen 7) mit ± 5% Impedanzkontrolle für 112+ GHz Signale

-

3D Verbindungsoptimierung: Microvia -Arrays, die 0,15 mm²/mm Signaldichte ermöglichen, Konform mit PCIe Gen6 und CXL 3.0 Protokolle

Wärmezuverlässigkeitszertifizierung

Zertifiziert gemäß Mil-STD-883G-Standards, Die 124-Schicht 1,000+ Wärmezyklen (-55° C bis 125 ° C.) während der Pflege <1% Signalverlust bei 80 MPA -mechanische Belastung - ist ideal für Luft- und Raumfahrt- und Verteidigungsanwendungen.

Anwendungen: Beschleunigung der AI -Hardware- und Halbleiterförderung

AI -Server & Hochbandgedächtnis (HBM)

-

Signaldichte: 18% Erhöhung des Differentialpaar -Routings pro Schicht

-

Thermalmanagement: Kupfergefüllte Mikrovias verbessern die Wärmeleitfähigkeit durch 30%, kritisch für 500W+ KI -Beschleuniger

Tests auf Waferebene & 3D Verpackung

Ermöglicht die Genauigkeit der Sub-Micron-Ausrichtung (± 0,8 mm) und Signalverzögerungsregelung auf Pikosekundenebene für gestapelte HBM-Module-ein Game-Changer für Chiplet-basierte Architekturen.

Kostenherausforderungen & Skalierbarkeit Roadmap

Fertigungsökonomie

-

Materialkosten: 4,800/M2(vs.3,200/M² für 108-Schicht)

-

Ertragsraten: 65% (16-Wochenzyklus) vs. 85% für konventionelle HDI

-

Fehleranalyse: Destruktives Querschnitt erforderlich für 20% von thermischen Stressfehlern

Industrielle Adoptionswege

-

Additive Fertigung: Reduziert die Laminierungsschritte durch 40%

-

AI-gesteuerte Eda: Prognostiziert über Stresspunkte mit 92% Genauigkeit, potenziell steigern die Erträge auf 75%

Marktausblick: $49B PCB -Industrie Transformation

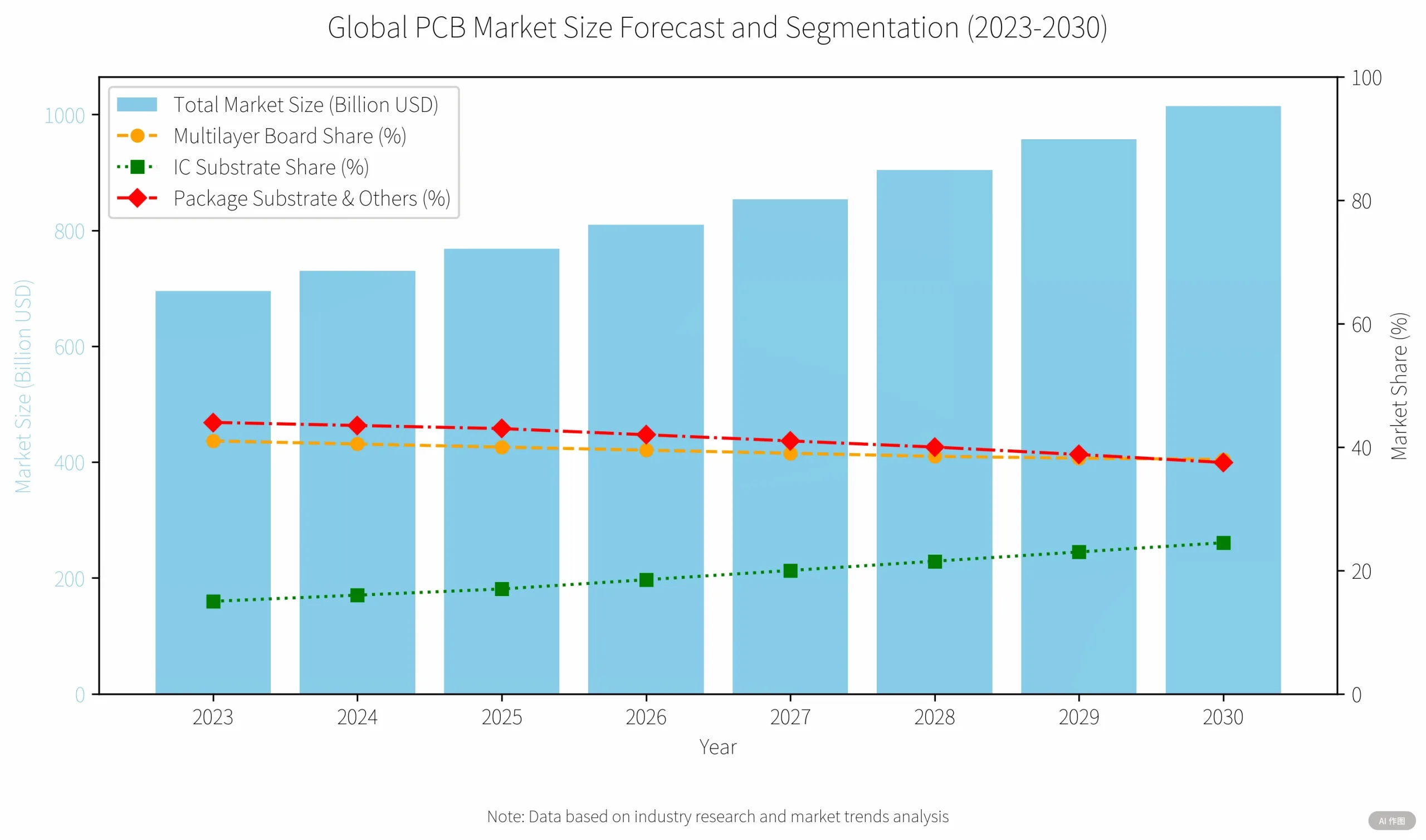

Wachstumstreiber

-

Cloud Computing: 70% CAGR in AI Server PCBs (Citic Securities 2026 Vorsprung)

-

Edge AI -Geräte: 30% PCB-Kostenanstieg bei Smartphones der nächsten Generation (Apples Lieferkettendaten)

-

Lokalisierungstrends: Chinesische Hersteller mögen UGPCB Targeting von 3,6 m² pro Jahr Kapazität für fortschrittliche Substrate

Abschluss: Praktische Innovation über Schichtzahlaufzeichnungen

Ohne den 129-layer-Prototyp von Denso nicht zu übertreffen (2012), Dieser 124-Layer-PCB setzt einen neuen kommerziellen Benchmark durch:

-

Standardisierte Dicke (7.6mm) Für die Rückwärtskompatibilität

-

MIL-Spec-Zuverlässigkeit bei 85% der Prototypkosten

-

Skalierbare Herstellungsprozesse

Als Quantencomputer und 6G tauchen auf, PCB -Innovation wird die Funktionsdichte gegenüber der Schichtzahl priorisieren - eine entscheidende Verschiebung für nachhaltigen technologischen Fortschritt.

UGPCB-LOGO

UGPCB-LOGO