Beherrschen der PCB -Impedanzkontrolle: Fortgeschrittene Strategien für das Hochgeschwindigkeitsschaltungsdesign

Figur 1: Kritische Impedanz-kontrollierte Spuren im Mehrschicht-PCB-Design

Die kritische Rolle der Impedanzkontrolle in der modernen Elektronik

Warum Impedance-Matching-Angelegenheiten bei Hochfrequenzentwürfen wichtig sind

In hochgeschwindigen digitalen Systemen, die oben arbeiten 1 GHz, Leiterplatte Spuren verwandeln sich von einfachen Leitern zu komplexen Übertragungsleitungen, bei denen charakteristische Impedanz (Z₀) wird von größter Bedeutung. Wenn Z₀ -Fehlanpassungen zwischen den Komponenten auftreten, Signalreflexionen können erreichen 35% von Incident Power, Verursacher von Wellenformverzerrungs- und Timing -Fehlern, die die Systemleistung verkrüppelten.

Schlüsselsequenzen einer schlechten Impedanzkontrolle:

- Signalintegritätsverschlechterung: Zunahme Verschlechterung bis zu 40% In DDR4 -Schnittstellen

- EMI -Strahlungsspitzen: Nicht übereinstimmende Linien können die gestrahlten Emissionen um 15-20 dB erhöhen

- Probleme mit der Kraftintegrität: Rücklaufpfaddiskontinuitäten erzeugen Bodensprung

Grundlegende Impedanzkonzepte

Charakteristische Impedanzformel für Microstrip:

Z₀ = frac{87}{\sqrt{E_R + 1.41}} \ln links(\Frac{5.98H}{0.8W + T}\Rechts)

Wo:

- ε_r = dielektrische Konstante (FR4: 4.2-4.7, Rogers 4350b: 3.48)

- H = dielektrische Dicke (mm)

- W = Spurbreite (mm)

- T = Kupferdicke (oz)

Differentialpaarberechnung:

Z_{diff} = 2z₀ links(1 - 0.48e^{-0.96S/h}\Rechts)

S = Paarabstand, H = dielektrische Höhe

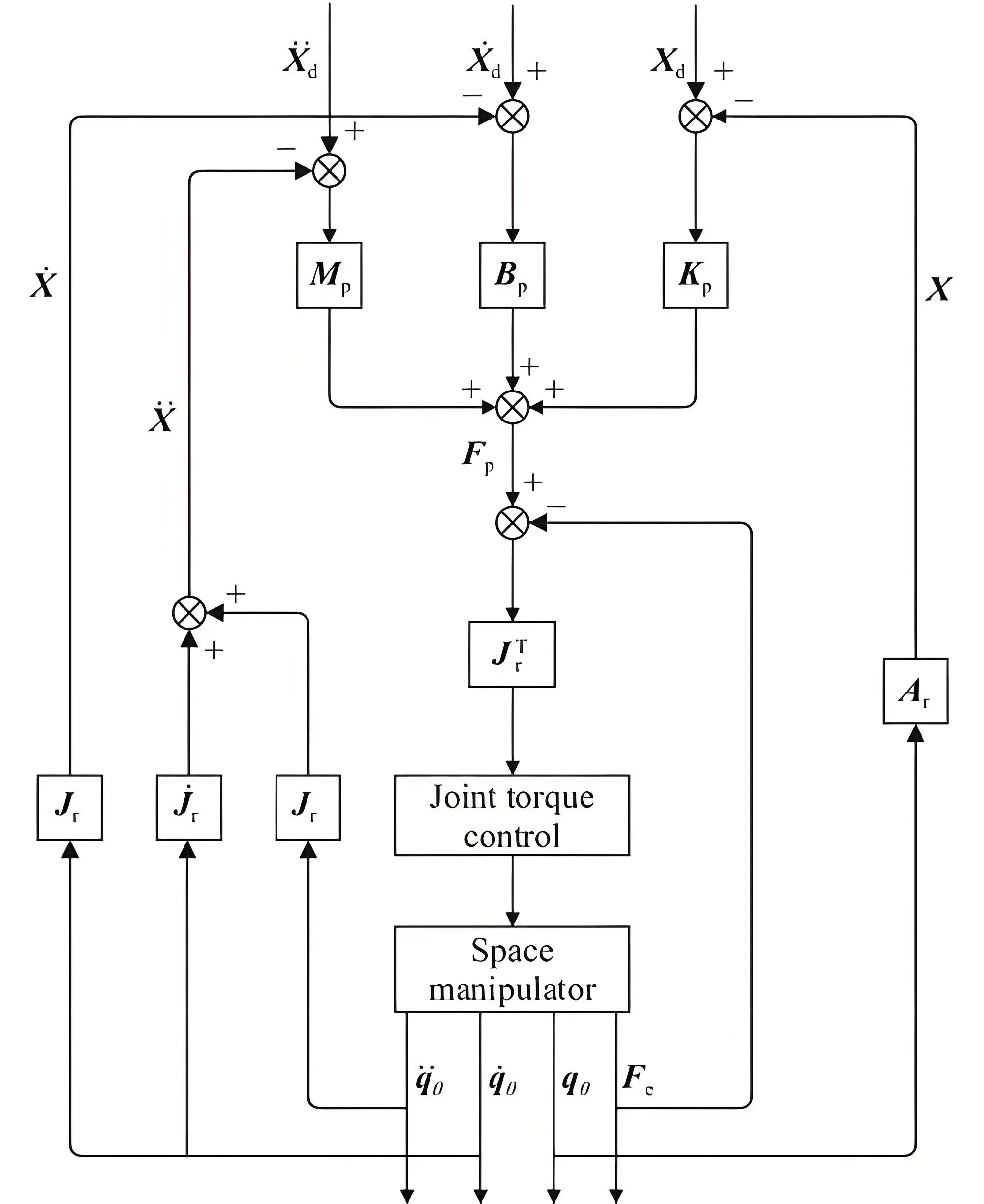

Fünf Säulen der PCB Impedance Engineering

1. Materialauswahlmatrix

| Materialtyp | ε_r @10ghz | Tangente Verlust | Kostenindex |

|---|---|---|---|

| FR-4 | 4.5 | 0.02 | $ |

| Rogers 4350b | 3.48 | 0.0037 | $$$ |

| I -Ra Island | 3.45 | 0.0031 | $$$$ |

| PTFE Composite | 2.2-3.0 | 0.0009 | $$$$$ |

Tisch 1: Hochfrequenz-Laminatvergleich

2. Prinzipien der Stackup -Architektur

Optimale 12-layer-HDI-Stackup für 25-Gbit / s-Signale:

- L1: Signal (0.5oz)

- L2: Boden

- L3: Signal (3.5mil dielektrisch)

- L4: Leistung

- L5: Signal (Hohe Geschwindigkeit)

- L6: Boden

… Spiegelsymmetrische Struktur

Kritische Parameter:

- Dielektrizitätstoleranz: ± 10% maximal

- Kupferrauheit: <2μm RMS für >10GHz

- Sequentielle Laminierung für die Impedanzkontinuität

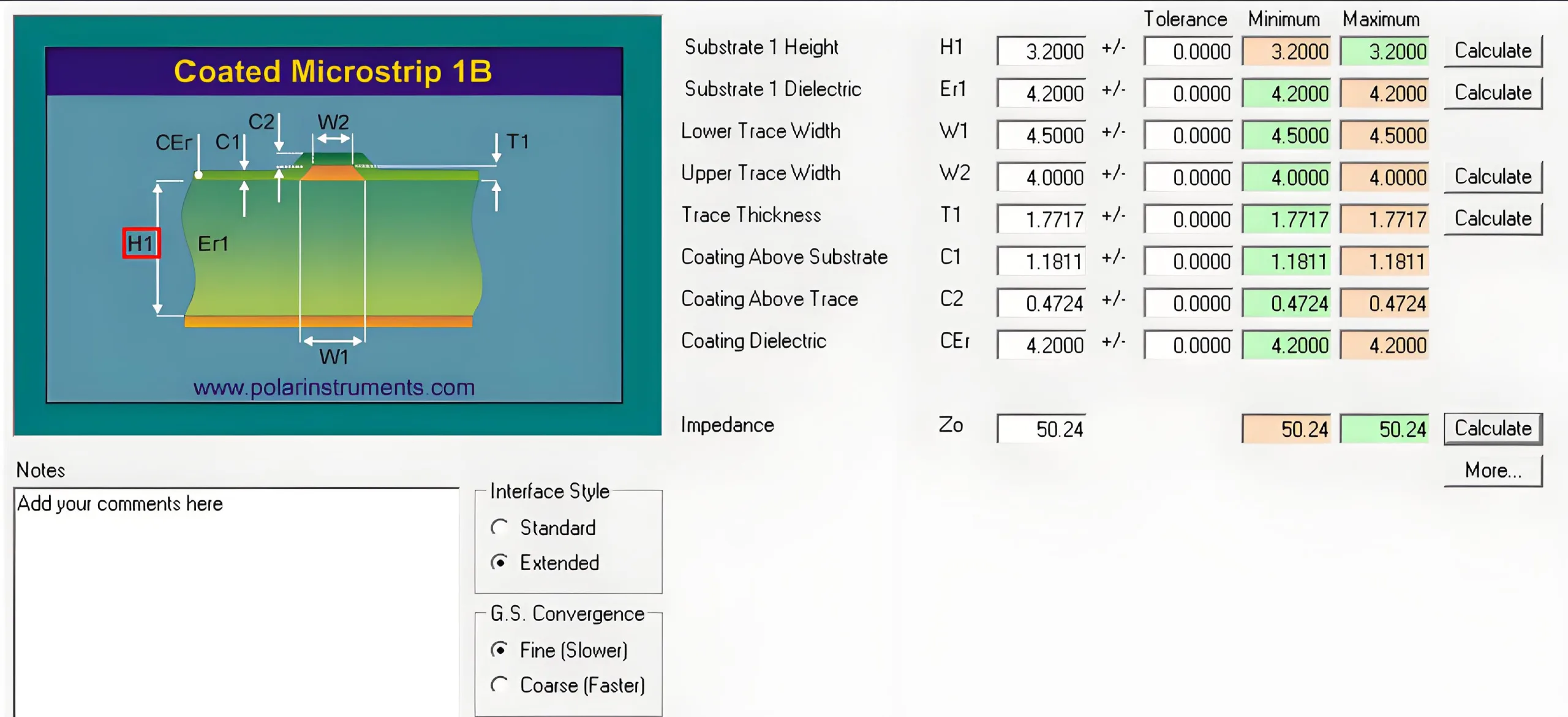

3. Erweiterte Berechnungsmethoden

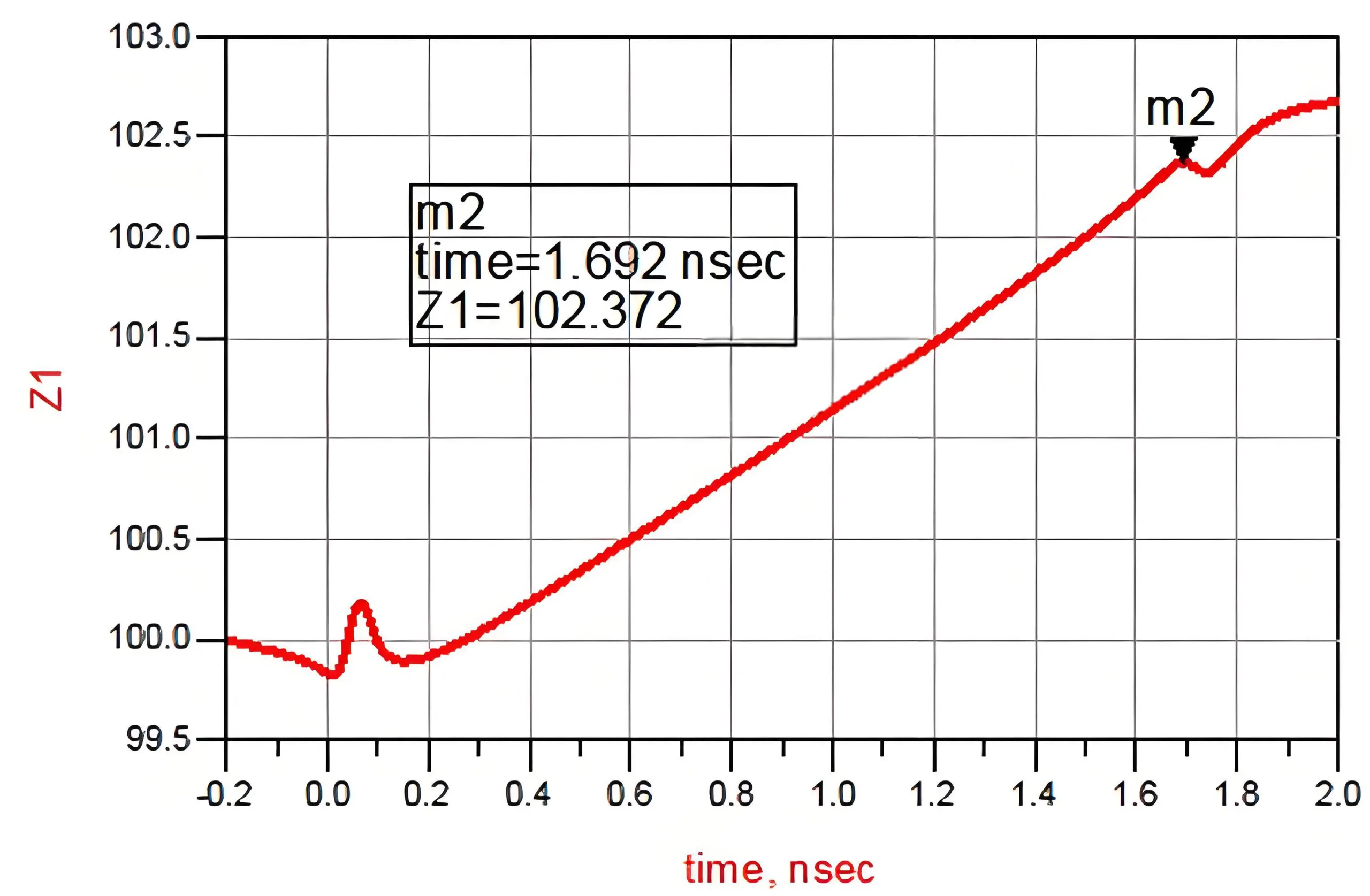

Dreistufiger Impedanz-Validierungsprozess:

- Anfängliche Schätzung:

Verwenden Sie empirische Formel:W pid frac{100H}{\sqrt{E_R}} \Quad (\Text{50Ω Microstrip}) - Präzisionssimulation:

- Polar SI9000 für mehrschichtige Strukturen

- Rogers MWI-2017 für RF/Mikrowellenlinien

- Überprüfung der Postproduktion:

TDR -Messungen mit <5% Toleranz

Figur 2: PCB Impedance Engineering Workflow

Figur 2: PCB Impedance Engineering Workflow

4. Herstellungsprozesssteuerung

Kritische Toleranzfaktoren:

| Parameter | Typische Toleranz | Auswirkungen auf z₀ |

|---|---|---|

| Ätzbreite | ± 0,5 Mio. | ± 3Ω |

| Dielektrische Dicke | ± 10% | ± 8 Ω |

| Kupfergewicht | 0,2 Unzen | ± 2 Ω |

| Soldata | 0.3-0.5Mil | ± 1,5o |

Daten aus IPC-2141A-Standards

Minderungsstrategien:

- Verwenden Sie kompensierte Kunstwerke (0.75× Ätzfaktor)

- Automatische optische Inspektion implementieren (AOI)

- Geben Sie kontrollierte Impedanz -Test -Gutscheine an

5. Spitzentools-Ökosysteme

Branchenführende Softwarelösungen:

- Polarinstrumente Si9000e

- 2D Feldlöser mit 47 Übertragungsleitungsmodelle

- Batch -Verarbeitung für komplexe Designs

- Rogers MWI-2017

- Spezialisiert für Mikrowellenkonstruktionen bis zu 110 GHz

- Integrierte Materialdatenbank mit 50+ Substrate

- Cadence Sigrity Aurora

- 3D Em Simulation mit <2% Fehlerrand

- DDR5/PCIE6.0 Compliance -Überprüfung

- Altiumimpedanzprofiler

- Echtzeitimpedanzvisualisierung

- Automatisierte Stackup -Validierung

Praktische Designrichtlinien für Ingenieure

Goldene Regeln für Erst-Rechts-Designs

- 3W -Regel für die Kontrolle über das Übersprechen:

S ≥ 3 × W Quad (\Text{Wo s = Spurabstand}) - Länge passende Prioritäten:

- Differentialpaare: <5MIL Intra-Pair Mismatch

- Bussignale: <100PS Verzögerung Scheck

- Über Optimierungstechniken:

- Verwenden Sie 8-12 Mio. Durchmesser für 10 Gbit / s-Signale

- Kulisse für Stublänge <15% der Anstiegszeit

- Kündigungsstrategien:

Typ Anwendung Stromkosten Serie 22 ω Quellend Niedrig Parallel 50 Ω Endpunkt Hoch Wechselstrom kapazitiv DDR -Speicherschnittstellen Medium

Zukünftige Trends im Impedanzmanagement

Aufstrebende Technologien wirken sich auf

- 5G mmwave Herausforderungen:

- 28/39GHz -Banden erfordern ± 1 Ω -Toleranz

- Laserablation für 2 & mgr; m Leitungsbreite Kontrolle

- Erweiterte Verpackungsintegration:

- 3D ic mit TSV -Impedanz -Matching

- Hybridsubstrat PCB-FLEX-Designs

- AI-gesteuerte Impedanzoptimierung:

- Neuronale Netze, die Herstellungsschwankungen vorhersagen

- Generatives Design für Multi-Constraint-Lösungen

Maßnahmen ergreifen, um ein Angebot zu erhalten

UGPCB Hält eine führende Position in beiden PCB (Leiterplatte) und pcba (Montage von Leiterplatten) Sektoren, Machen Sie es zu einem Branchenführer. UGPCB verfügt, Ranking an der Spitze der Branche. Wenn Sie Fragen oder Entwurfsanforderungen im Zusammenhang mit der PCB -Impedanz haben, Bitte wenden Sie sich an unser professionelles technisches Personal, um technischen Support zu erhalten, um Maßnahmen zu ergreifen und noch heute ein wettbewerbsfähiges Angebot anzufordern.

UGPCB-LOGO

UGPCB-LOGO