Briser les limites: À l’intérieur des capacités de conception de substrats IC de pointe de l’UGPCB

À l’ère de la puissance de calcul explosive de l’IA et de l’expansion de la bande passante 5G/6G, des puces de la taille d'un ongle intègrent désormais des milliards de transistors. Encore 60% des pannes de puces haut de gamme ne proviennent pas des plaquettes de silicium elles-mêmes, mais des défauts de leur support critique – le Substrat IC. Cette statistique surprenante souligne l’extrême importance de la conception du substrat.

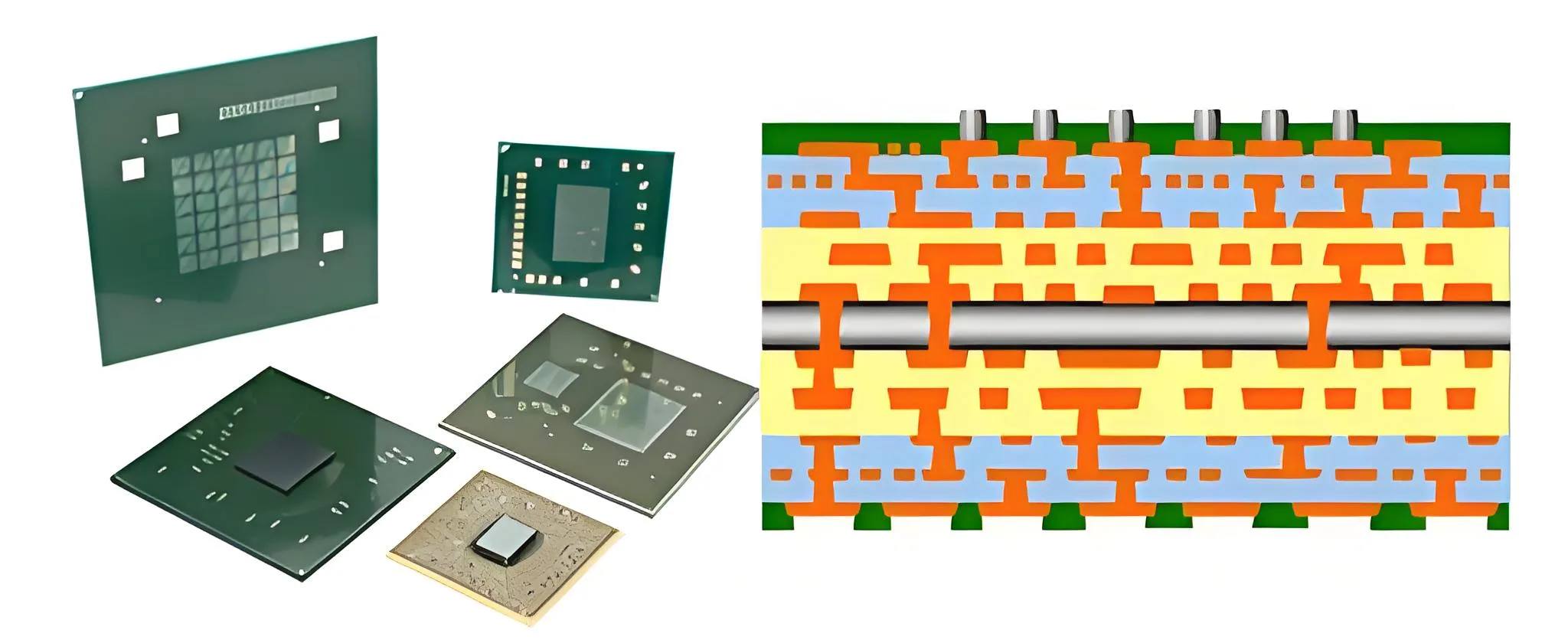

Substrats IC: Le fondement invisible de la performance des puces

Les substrats IC sont bien plus que de simples connecteurs; ils servent de centre neuronal et de noyau d'alimentation entre les puces et le monde extérieur. Avec un nombre d'E/S atteignant des milliers (même 10,000+ pour les GPU/CPU avancés), largeurs/espacement des traces rétrécissant en dessous de 15 μm/15 μm, et des vitesses de signal supérieures à 112 Gbit/s, la précision de conception fonctionne désormais à des échelles nanométriques. Défaillances de gestion thermique et dégradation de l’intégrité du signal sont devenus des tueurs majeurs dans le domaine de l'emballage avancé (2.5CI D/3D, Chiplet).

Formule clé: Précision du contrôle d'impédance (Z)

Z = (87 / √εr) × ln(5.98H / (0.8W + T))

Où εr = constante diélectrique, H = épaisseur diélectrique, W = largeur de trace, T = épaisseur du cuivre. L'UGPCB contrôle précisément ces paramètres pour atteindre une tolérance d'impédance de ± 5 %, dépassant la norme industrielle de ± 10 %.

Déconstruire les UGPCB 5 Capacités de conception de substrats IC de base

1. Interconnexion extrêmement haute densité (IDH) Conception

-

Maîtrise Microvia: Forage laser (<50µm) et un placage avancé permet HDI toutes couches. Améliore les canaux de routage en 40% dans les conceptions BGA au pas de 0,2 mm.

-

Percée de lignes ultra fines: La production en série de traces de 12 μm/12 μm répond aux exigences de pointe en matière de Chiplet.

-

Empilements avancés: Expertise 16+ conceptions de couches avec des matériaux hybrides (faible-Dk/Df + haute Tg) pour une intégration hétérogène.

2. Intégrité du signal/puissance à l’échelle nanométrique (SI/IP) Contrôle

-

3Simulation EM: Ansys HFSS et Cadence Sigrity éliminent les réflexions/diaphonie dans les canaux 112G PAM4.

-

Optimisation du PDN: Les réseaux de découplage distribué réduisent le bruit de l'alimentation électrique (PSN) par 60%.

-

Contrôle des pertes: Cuivre ultra discret (RTF / VLP) combiné à l'adhérence de la formule d'impédance, il minimise la perte d'insertion.

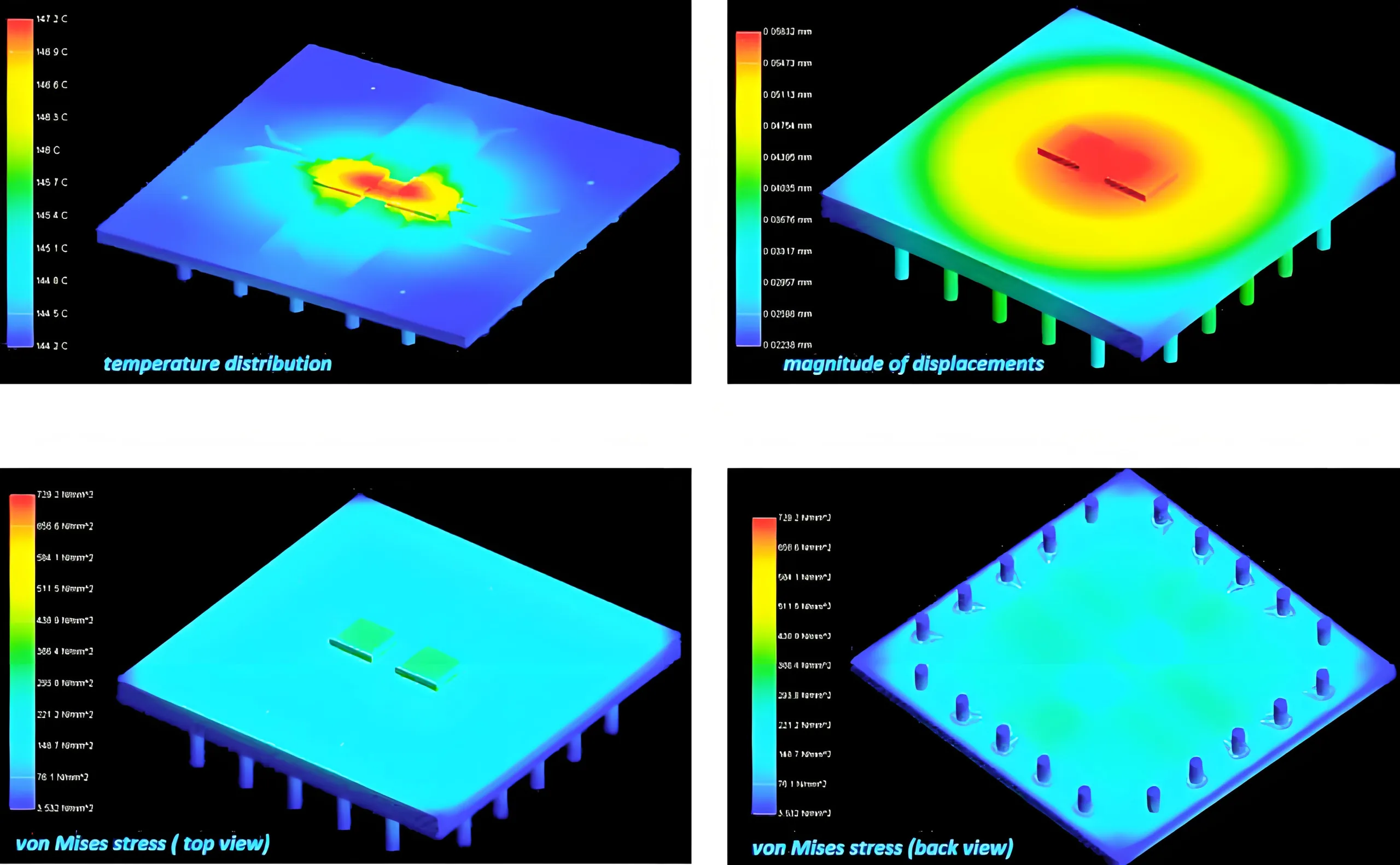

3. Fiabilité thermomécanique (TMV) Ingénierie

-

Correspondance CTE: Novateur matériels minimiser le gauchissement (<0.1%) en équilibrant la puce (~2,6 ppm/°C) et CTE du substrat (14-17 ppm/°C).

-

Simulation multiphysique: COMSOL prédit la fatigue des joints de soudure pendant le cycle thermique.

-

Architecture thermique: Caloducs intégrés + >5 W/mK TIM + des vias thermiques optimisés améliorent le refroidissement du système.

4. Emballage avancé en co-conception

-

Collaboration Fab/OSAT: Intégration précoce de DFM pour FCBGA, WLP, and Si interposer processes.

-

Expertise en chiplets: Bande passante élevée conforme à l'UCIe, interconnexions à faible latence.

-

Science des matériaux: Utilisation stratégique d'Ajinomoto ABF, Série MEGTRON pour les besoins RF/thermiques/fiabilité.

5. Conception basée sur DFM/DFT

-

Fabricabilité intégrée: Les règles de conception alignées sur les capacités du processus maximisent le rendement au premier passage (FPY).

-

Optimisation de la testabilité: Dispositions de points de test compatibles ATE pour les substrats complexes.

-

Conception pour le rendement (DFY): L'équilibrage du cuivre et la compensation de gravure améliorent la cohérence de la production.

Histoire de réussite de l'UGPCB: De la conception à la production de masse

Cas: Substrat FCBGA pour accélérateur d'IA haute puissance

-

Défi: 45Matrice ×45 mm, >800Puissance W, 56Signaux Gbps PAM4 nécessitant des performances thermiques/électriques extrêmes.

-

Solution:

-

16-couche n'importe quelle couche IDH avec traces 12μm/12μm

-

Est tombé 7 cœur (εr=3,3, Df=0,001) + contrôle d'impédance de précision

-

Blocs de cuivre intégrés + réseaux de micro-vias (35% réduction de la résistance thermique)

-

Co-conception avec OSAT pour l'optimisation des bosses/itinéraires

-

-

Résultat: Validation SI/PI/thermique réussie pour la première fois, 98.5% rendement, 6-délai de mise sur le marché plus rapide d'un mois.

Pourquoi les leaders mondiaux choisissent l'UGPCB comme partenaire de substrat IC

Avec 100+ ingénieurs experts, 300+ conceptions annuelles de substrats IC, 20+ brevets, et des laboratoires de simulation de plusieurs millions de dollars, UGPCB délivre:

Différenciateurs clés

-

Leadership technologique: Définir les limites des substrats de nouvelle génération via R&D.

-

Solutions de bout en bout: Conception → Prototype → Production en volume sous un même toit.

-

Certitude de fabrication: Les usines de fabrication avancées en interne garantissent la réalisation des intentions de conception.

-

24/7 Réactivité: Des équipes d'assistance dédiées avec des devis instantanés.

Libérez tout le potentiel de votre puce dès aujourd’hui!

Votre puce phare de nouvelle génération est-elle limitée par les goulots d'étranglement du substrat? Les experts de l’UGPCB sont prêts à apporter:

✅ Évaluation gratuite de la faisabilité de la conception de substrats IC

✅ Devis compétitifs pour solutions PCBA en 24 Heures

[Contactez dès maintenant les experts en substrats IC de l'UGPCB pour une assistance instantanée & Citation]

LOGO UGPCB

LOGO UGPCB

WeChat

Scannez le code QR avec WeChat