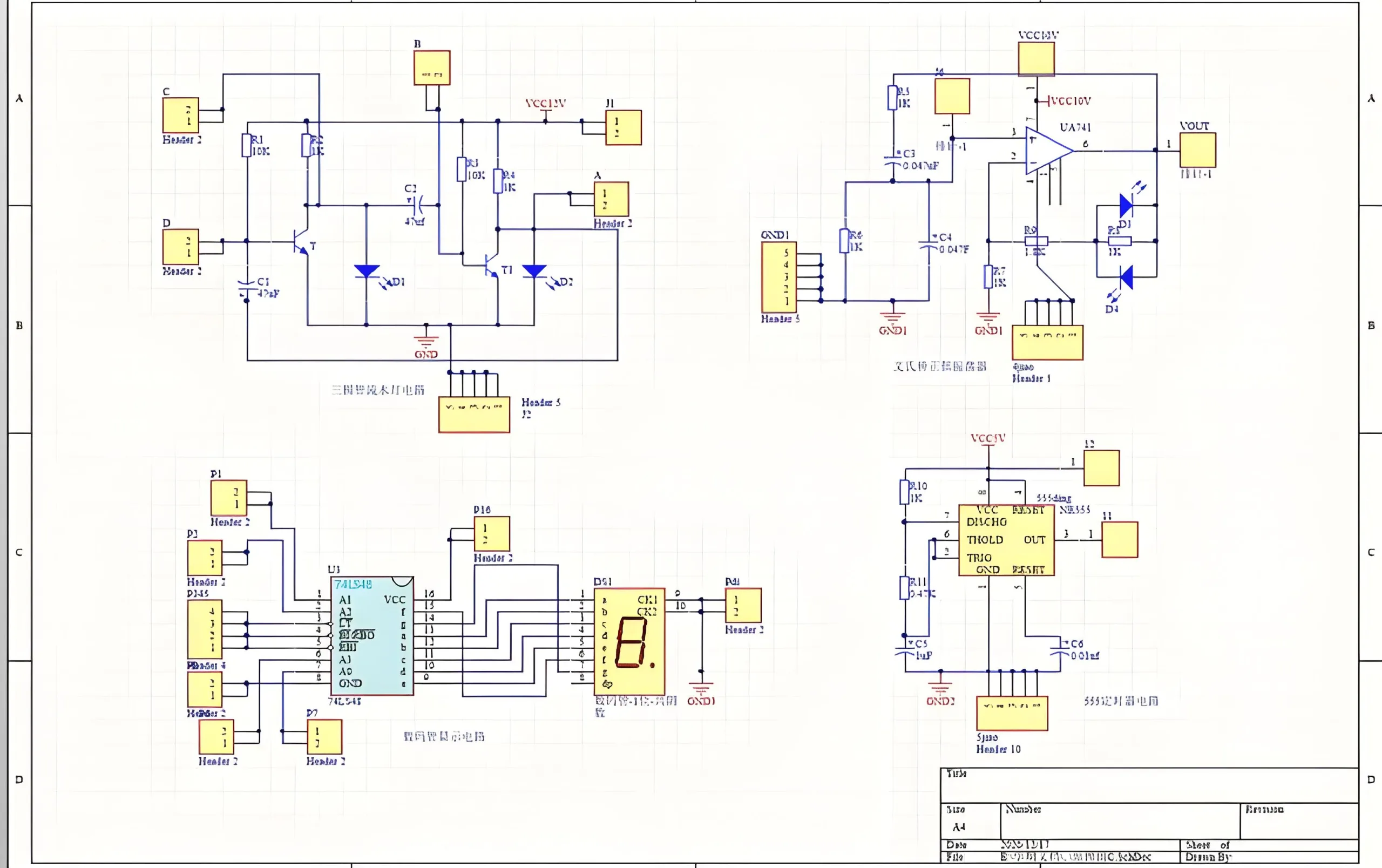

A la convergence des circuits numériques haut débit et des systèmes analogiques de précision, un design exquis PCB schématique détermine la viabilité du produit – avec 90% des défaillances de conception provenant de l'effondrement de l'intégrité de l'alimentation électrique.

Lorsque les ingénieurs acheminent la 37e trace DDR4 de longueur correspondante dans Altium Designer, impédance les discontinuités cachées dans les piles de couches dégradent silencieusement l'intégrité du signal. Les données de simulation de l’UGPCB révèlent: Les PCB avec des modules d'alimentation non optimisés en souffrent 62% taux d'échec, tandis que les conceptions mettant en œuvre notre technologie à plan divisé réduisent les taux d'erreur binaire à 10⁻¹²..

L'essence des circuits: Principes fondamentaux des schémas PCB & Évolution

Des schémas de câblage aux systèmes intelligents

Les schémas modernes ont évolué vers écosystèmes d'ingénierie intelligents:

-

Réseaux de neurones électriques: Intégrer 32 règles de conception (seuils de largeur de trace/espacement/impédance/diaphonie); Le gestionnaire de contraintes de l'UGPCB se synchronise 12,000+ réseaux

-

Collaboration inter-domaines: L'analyse Allegro SI montre Marge de synchronisation de ± 18 ps pour les chemins critiques en 6 couches Cartes HDI, nécessitant une co-optimisation schématique-PCB-firmware

Avancées révolutionnaires des outils de conception

| Génération d'outils | Logiciel représentatif | Gain d'efficacité | Cas d'optimisation UGPCB |

|---|---|---|---|

| Conception fondamentale | Protel99SE | 1X Référence | Compatibilité des bibliothèques héritées pour la migration de projets |

| Conception à grande vitesse | Concepteur avancé | 3.2X | Erreur de correspondance de longueur dynamique ≤0,01 mm |

| Conception du système | Cadence Allegro | 5.7X | 40% amélioration de la marge du diagramme oculaire à 16 Gbit/s |

Étude de cas UGPCB: La migration d'OrCAD vers Allegro a augmenté le succès du routage d'évacuation BGA depuis 74% à 98%, réduire les cycles de développement en 21 jours.

Méthodologie de conception modulaire: Déconstruire les circuits complexes

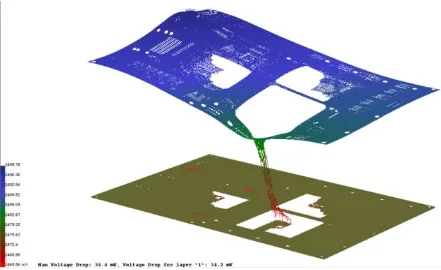

Intégrité de puissance: Le différenciateur critique

Formule de sélection de topologie:

η = \frac{P_{dehors}}{P_{dehors} + P_{sw} + P_{cond}} \quad \text{(Cible h>92\%)}

UGPCB 3Analyse de l'arbre de puissance D:

-

Chute de tension réduite de 220 mV à 35 mV dans l'ECU automobile via Optimisation du placement LDO

-

Avions à propulsion hybride: Les techniques de plans divisés/mixtes ont réduit l'ondulation de 67%

Contrôle de précision des chemins de signaux à grande vitesse

Équation de contrôle d'impédance:

Mise en œuvre de l'UGPCB:

-

Compensation différentielle des paires: Obliquité obtenue<2ps dans les modules optiques 100G

-

Murs de blindage EM: 18Amélioration du SNR en dB médical PCB via isolation numérique/analogique

Conception de qualité industrielle: UGPCB 9 Technologies de base

3Optimisation de l'architecture d'empilage

Configuration optimale à 8 couches:

L1: Signal (Grande vitesse) L2: Solid GND L3: Signal (Stripline) L4: Power L5: GND L6: Signal L7: Power L8: Signal (Basse vitesse)

Validation: 12Réduction EMI dBμV/m, Certifié FCC Classe B

Conception axée sur la fabrication (DFM) Précision

UGPCB Contrôle de processus ±0,025 mm:

-

Technologie microvia: 0.1forets laser mm, 12:1 rapport d'aspect

-

Épaisseur du cuivre: Tolérance de gravure de ± 10 % pour les couches externes de 2 oz

-

Ponts de masque de soudure: 0.075La largeur minimale de mm empêche le pontage SMT

Au-delà du design: Services de cycle de vie complet de l’UGPCB

Assurance de l'intégrité du signal

Phase de conception: La simulation de pré-mise en page HyperLynx élimine 90% risques

Phase de validation: Les tests TDR garantissent <5% écart d'impédance

Production de masse: Base de données de référence dorée pour le contrôle des paramètres clés

Intégration de la fabrication intelligente

Résultats: 48-livraison du prototype en une heure, 99.2% rendement de premier passage

Laboratoire du futur: Les frontières technologiques de l’UGPCB

Intégration hétérogène de substrat de silicium

2.5Interposeurs D TSV:

-

0.3interconnexions au pas de mm pour l'intégration FPGA-HBM

-

Résistance thermique réduite à 0,15°C/W

Révolution EDA pilotée par l'IA

Moteur NeuroRoute:

-

8Amélioration de l'efficacité du routage X

-

Fonction d'optimisation:

Min(ΔL, Crosstalk, Via_Count) -

Déployé dans un réseau d'antennes 5G mmWave PCB dessins

LOGO UGPCB

LOGO UGPCB

WeChat

Scannez le code QR avec WeChat