Компоновка печатной платы: The Critical Battleground for Electronic System Performance

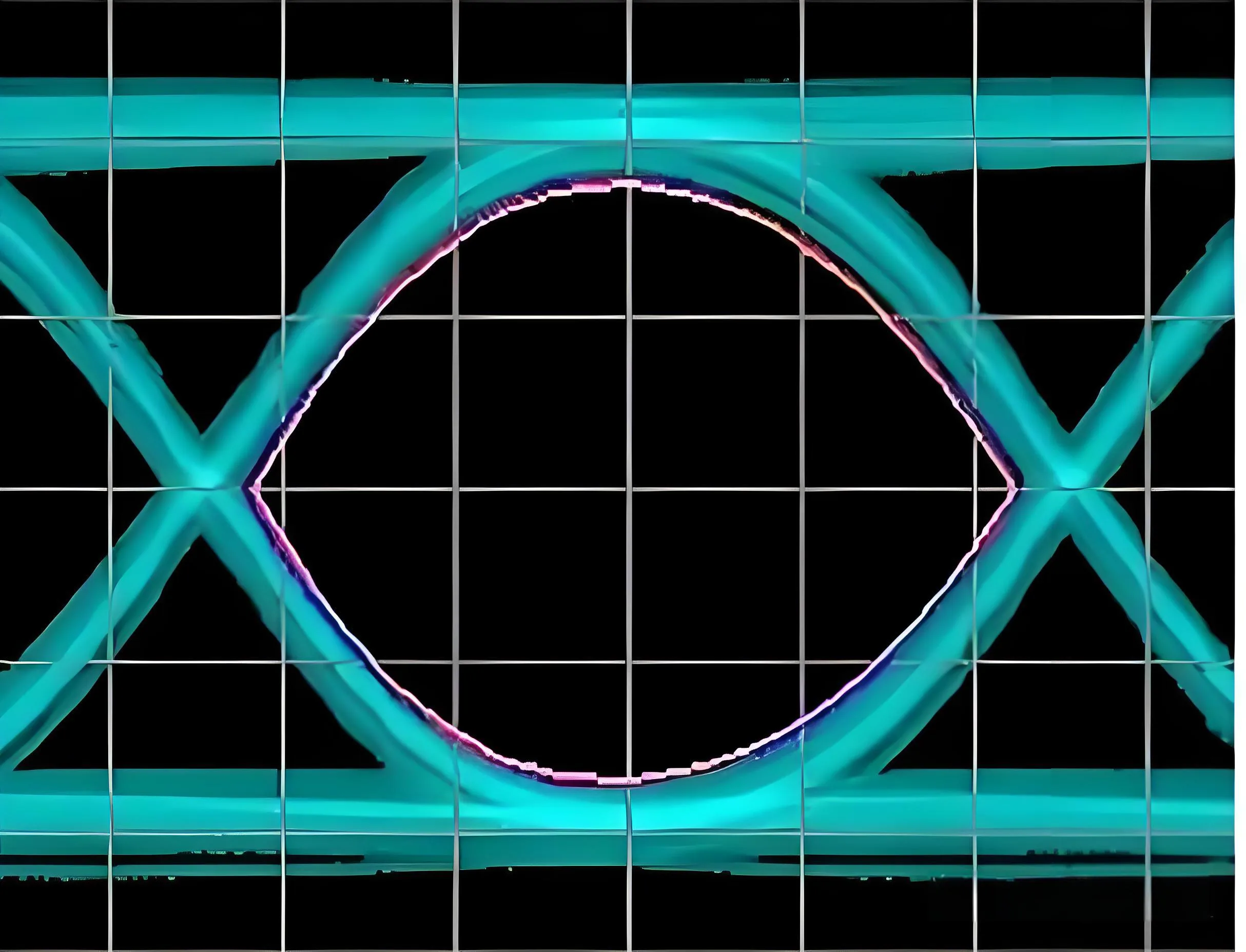

Пекс печатной платы трансцентирует подключение к физической цепи, фундаментально определение целостности сигнала, EMC performance, и экономическая эффективность. УГКПБ data confirms: оптимизированные макеты уменьшают радиацию EMI на 30% (МЭК 61000-4-2 соответствие) и повысить эффективность мощности 22%. Для сигналов, превышающих 5 Гбит / с, Допустимость импеданса должна контролироваться в пределах ± 5% (Формула: Z₀ = √(L/C.)), Требование строгого дизайна стека PCB и выбора материалов.

7 Основные технологии: Методология макета UGPCB

-

Высокоскоростная обработка сигнала (1.5-28Гбит / с)

-

Соответствие дифференциальной пары длины: ± 5 миль точности

-

Контроль потерь: Упал 6 субстрат (Дк=3.7, Дф= 0,002) Для сигналов 28 Гбит / с

-

-

Инновации в области целостности власти

Оптимизированный импеданс PDN с помощью 3D EM -симуляции:Целевой импеданс формула: Z_target = (V × Ripple%) / (Я × 50%)Тематическое исследование: Раствор мощного раствора основного графического процессора пониженные колебания напряжения с 120 мВ до 35 мВ

-

Стратегия разбиения смешанного сигнала

-

Цифровое/аналоговое расстояние: ≥8 × толщина доски

-

Автомобильные решения: Расположение компонентов AEC-Q100 с ISO 26262 сертификация

-

Решения в отрасли Pain Point

Проблемы дизайна HDI в потребительской электронике

| Испытание | Решение UGPCB | Результат |

|---|---|---|

| 0.2MM Microvia Fill | Лазерное бурение + пульсовое покрытие | 99% урожайность |

| 5G Wi -Fi Interference | 3D EM shielding design | 40% нижний бер |

История успеха: 48-Дизайн материнской платы сервера слоя

-

Ключевые спецификации:

-

Слои сигнала: 32

-

Дифференциальные пары: 287 наборы

-

Управление временем: ± 12 л.с.

-

-

Demonstrated outcome:

*”PCIE 4.0 Потеря сигнала снизилась с -8,2 дБ до -5,3 дБ, Ускорение массового производства 11 недели”*

- отзывы клиента HPC

Почему выбирают услуги макета UGPCB?

-

Экспертная команда: Инженеры с 10+ годы’ experience averaging 800+ Высокоскоростные дизайны

-

Сквозная поддержка:

-

Схематическая конструкция → SI/PI Моделирование → Оптимизация макета → Валидация DFM → PCBA Co-Design

-

-

Контроль затрат: 15% экономия материала с помощью оптимального планирования слоя

ЛОГОТИП УГКПБ

ЛОГОТИП УГКПБ

Вичат

Сканируйте QR-код с помощью WeChat