„Warum werden Späne beschädigt, wenn ich nur damit umgehe?“ Leiterplatte normalerweise?„Viele Ingenieure sind verwirrt, wenn sie mit Stromkreisschäden konfrontiert werden, die durch elektrostatische Entladung verursacht werden (ESD). Tatsächlich, Der menschliche Körper kann elektrostatische Spannungen von bis zu mehreren Zehntausend Volt erzeugen – weit über der Toleranzgrenze der meisten elektronischen Komponenten.

Selbst höchste Präzision Leiterplatten (Leiterplatten) können anfällig für ESD sein. Eine versehentliche Berührung kann dazu führen, dass Chips im Wert von mehreren Tausend Dollar sofort kaputt gehen.

Vor dem Hintergrund immer anspruchsvollerer elektronischer Geräte von heute, ESD-Schutz ist keine optionale Wahl mehr, sondern eine notwendige Maßnahme zur Gewährleistung der Produktzuverlässigkeit. In diesem Artikel werden die wichtigsten Designpunkte und Herstellungskriterien des PCB-ESD-Schutzes eingehend analysiert, Helfen Sie Ihren Produkten, diesem „unsichtbaren Blitz“ zu widerstehen.

1. ESD-Bedrohungen: Die tödliche Wirkung unsichtbarer Miniaturblitze

ESD kann man sich wie einen unsichtbaren Miniaturblitz vorstellen. Tägliche Aktivitäten wie Spazierengehen, Pullover ausziehen, oder sogar das Anheben einer Plastikbox kann statische Elektrizität erzeugen. Die Spannung dieser statischen Elektrizität erreicht oft mehrere tausend Volt, oder sogar Zehntausende Volt.

Der menschliche Körper selbst ist tatsächlich der größte Erzeuger statischer Elektrizität. Vor allem in Trockenzeiten, ESD kann auftreten, sobald Sie nach einer Leiterplatte greifen. Scheinbar unbedeutende Gegenstände wie Plastik-Desktops, Teppiche aus Chemiefasern, und Schaumstoffverpackungen können alle zu „Komplizen“ statischer Elektrizität werden.

ESD schadet Leiterplatten in zwei Hauptformen:

- Harter Schaden: Dies ist der direkteste und offensichtlichste Schaden. Durch ESD werden die winzigen Schaltkreise im Chip sofort zerstört, Dadurch wird der Chip dauerhaft beschädigt. Infolge, Die Platine funktioniert dann überhaupt nicht mehr, oder bestimmte Funktionen (wie serielle Schnittstellen oder ADCs) wird direkt scheitern.

- Chronischer Schaden: Dies ist versteckter und problematischer. ESD zerstört den Chip möglicherweise nicht vollständig, Es kann jedoch zu Mikroschäden an inneren Oxidschichten und anderen Strukturen führen. Möglicherweise funktioniert die Platine jetzt noch normal, aber es wird instabil und hat eine verkürzte Lebensdauer. Nach einigen Tagen oder bei bestimmten Temperaturen kann es zu plötzlichen Fehlfunktionen kommen. Dieser zeitweilige Fehler ist beim Debuggen am schwierigsten zu beheben und erfordert viel Zeit und Mühe.

2. TVS-Dioden: Das Präzisions-Blitzschutzsystem für Stromkreise

Fernseher (Überspannungsschutz) Dioden sind die erste Verteidigungslinie gegen ESD-Bedrohungen und die wirksamsten Schutzkomponenten. Sie fungieren wie „Sicherheitswächter für Schaltkreissignale“ und halten unter normalen Bedingungen einen hochohmigen Zustand aufrecht. Sobald ein ESD-Impuls erkannt wird, Sie wechseln sofort in einen niederohmigen Zustand, Leiten Sie den Hochspannungsimpuls zur Erde um und schützen Sie die Backend-Chips.

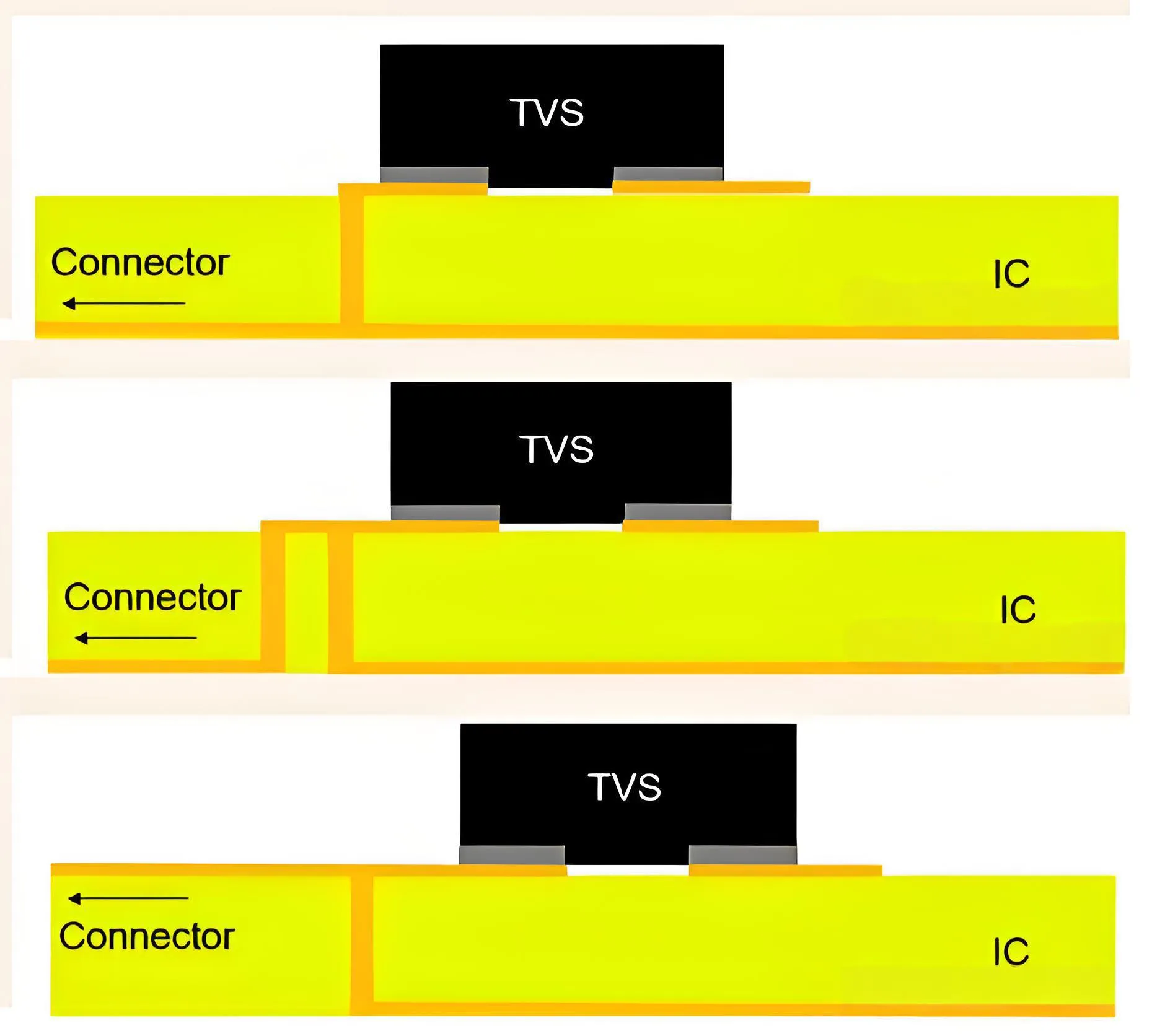

2.1 Goldene Regeln für das TVS-Layout

Parasitäre Induktivität ist der größte Feind der TVS-Leistung. Parasitäre Induktivität im Schaltkreis – einschließlich der parasitären Induktivität der TVS-Pins selbst – beeinflusst die Klemmspannung (Vc) am Backend-IC, wenn ESD oder Überspannungen auftreten.

Die Schutzwirkung von TVS folgt der Formel: VCL = VBR + RD × IPP. Darunter:

- RD ist die parasitäre Kapazität des TVS selbst; Produkte mit kleineren RD-Werten haben eine bessere Klemmspannung und können ICs wirksamer schützen.

- IPP ist der Strom, der während des Testzeitpunkts durch das TVS fließt.

Um die Schutzwirkung von TVS zu maximieren, Sie müssen sicherstellen, dass die Erdungsverbindung so kurz wie möglich ist und das TVS so nah wie möglich an der ESD-Quelle platzieren. Dies minimiert nicht nur EMI (Elektromagnetische Interferenz) auf der Leiterplatte, reduziert aber auch die Kopplung mit anderen Pfaden. Die Wahl eines TVS-Geräts mit einer Reaktionszeit von weniger als 1 ns bietet optimalen Schutz für Hochgeschwindigkeitsschnittstellen – entscheidend für PCBA (Montage von Leiterplatten) Zuverlässigkeit.

3. PCB-Layout und Erdung: Die Grundlage des ESD-Schutzes

Vernünftig PCB-Layout und Erdungsdesign sind die Eckpfeiler des ESD-Schutzes. Auch ohne zusätzliche Schutzkomponenten, Sie können die ESD-Festigkeit des Produkts deutlich verbessern.

3.1 Wichtige Punkte für das PCB-Layout

- Hochgeschwindigkeitssignalleitungen sollten ≥3 mm vom Platinenrand entfernt sein, während niederfrequente empfindliche Signale ≥2 mm entfernt sein sollten.

- Kritische Signale wie Taktleitungen und Reset-Leitungen sollten von Masse umgeben sein (Erdungsabschirmung). Ordnen Sie Erdungsleitungen auf beiden Seiten an und fügen Sie alle 50 mm Erdungsdurchkontaktierungen hinzu.

- Alle freiliegenden Metallgehäuse müssen einpunktig über einen 1-MΩ-Widerstand geerdet werden, um die Bildung einer Schleife mit niedriger Impedanz durch direkte Erdung zu vermeiden.

- Zwischen Komponenten, die mit dem Benutzer in Berührung kommen, sollte eine Kriechstrecke von ≥5 mm eingehalten werden (wie Knöpfe und Knöpfe) und die Hauptplatine. Verwenden Sie leitfähigen Schaumstoff oder Metallfedern, um eine Potenzialausgleichsverbindung herzustellen.

- Funkenstrecken einstellen (mit einem Abstand von 0,2 mm–0,5 mm) an der Pin1-Position des Steckers und dem Erdungspunkt des Metallgehäuses. Diese Maßnahmen können den ESD-Strom effektiv in eine sichere Entladung leiten und Schäden an empfindlichen Schaltkreisen vermeiden.

3.2 Prinzipien für das PCB-Erdungsdesign

Bei der Gestaltung von Doppelschicht- bzw Multi-Layer-PCBs, Versuchen Sie, eine vollständige und großflächige Grundfläche sicherzustellen. Eine vollständige Grundplatte ist wie eine ausgedehnte Ebene – sie kann ESD-Energie schnell absorbieren und zerstreuen, verhindert, dass sich Energie an einem einzigen Punkt ansammelt. Gleichzeitig, Es bietet einen effizienten Entladepfad für TVS-Dioden.

Während des PCB-Layouts, Füllen Sie das Erdungsnetzwerk mit Kupfer und stellen Sie sicher, dass das Erdungskupfer möglichst viel des leeren Bereichs auf der Platine bedeckt (ohne Spuren) wie möglich. Für alle externen Schnittstellen (wie USB-Anschlüsse und Gleichstromsteckdosen), Verbinden Sie das Metallgehäuse über einen Hochspannungskondensator oder direkt mit der Masse der Platine. Hier entlang, ESD wird zuerst durch das Gehäuse abgeleitet, bevor sie in den Schaltkreis gelangt. Dadurch wird der ESD-Schutz der Leiterplatte auf Schnittstellenebene verbessert.

4. Laminierungsprozess: Die interne Schutzbarriere für mehrschichtige Leiterplatten

In mehrschichtigen Leiterplatten, Die Qualität des Laminierungsprozesses steht in direktem Zusammenhang mit der internen ESD-Schutzfähigkeit der Platine. Wenn das Dielektrikum zwischen zwei Leiterschichten zu dünn ist, Hochspannungs-ESD kann es leicht beschädigen, bleibenden Schaden verursachen.

4.1 Kernrolle von Prepreg

Prepreg (vorimprägniertes Verbundmaterial) fungiert als Zwischenschicht-Isolierdielektrikum in mehrschichtigen Leiterplatten. Es handelt sich um einen „funktionalen Verbundwerkstoff“, der durch Präzisionsfertigungsprozesse kontrolliert wird, Sein Hauptmerkmal besteht darin, dass sich das Harz im „halbgehärteten B-Stadium“ befindet – eine Eigenschaft, die für die Realisierung einer mehrschichtigen Plattenlaminierung von entscheidender Bedeutung ist.

Prepreg sorgt nicht nur für eine physikalische Verbindung, sondern erzielt auch drei Effekte: elektrische Isolierung + strukturelle Unterstützung. Seine Isolationsleistung und dielektrischen Eigenschaften bestimmen direkt die elektrische Zuverlässigkeit der Leiterplatte: nach dem Aushärten, der Volumenwiderstand beträgt ≥10¹⁴Ω·cm, und die Durchbruchspannungsfestigkeit beträgt ≥20 kV/mm, Dies kann Leckagen zwischen den Schichten blockieren – entscheidend für die Verhinderung von ESD-bedingten Schäden zwischen den Schichten.

Zu den Kernparametern von Prepreg gehören::

- Harzgehalt (RC%): Normalerweise 50 % ~ 70 %, Dies bestimmt die Bindungsstärke zwischen den Schichten und die Dicke der dielektrischen Schicht.

- Fließfähigkeit: 15~30mm.

- Glasübergangstemperatur (Tg): Normalerweise 150~200℃.

- Dielektrizitätskonstante (Dk): 4.2±0,2 für gewöhnliches FR-4 Prepreg.

4.2 Qualitätskontrolle für den Laminierungsprozess

Um die Qualität der Laminierung sicherzustellen, der Wärmeausdehnungskoeffizient (CTE) Die Stärke des Prepregs muss mit der von FR-4-Trägerplatten und Kupferfolien übereinstimmen. Wenn die CTE-Abweichung der Z-Achse 5 ppm/℃ überschreitet, Während des Temperaturwechsels kann es wahrscheinlich zu Zwischenschichtrissen kommen.

Während der Laminierung:

- Wenn die Temperatur der mittleren Schicht 80 bis 130 °C beträgt, Der Temperaturunterschied zwischen der oberen Schicht der Trägerplatte und der mittleren Schicht sollte 25 °C nicht überschreiten, und die Heizrate sollte 1,3~5℃/min nicht überschreiten.

- Wenn die Temperatur 85 ± 5 °C erreicht, Bestimmen Sie die Zeit zum Umschalten von Niederdruck auf Mitteldruck.

- Wenn die Temperatur 110 ± 5℃ erreicht, Bestimmen Sie die Zeit zum Umschalten von Mitteldruck auf Hochdruck.

In der modernen Leiterplattenfertigung, Die Vakuumpresstechnologie hat die Laminierqualität deutlich verbessert. Die Vakuumumgebung verhindert die Bildung von Blasen und Hohlräumen, Gewährleistung eines gleichmäßigen Flusses und Füllens des Prepreg-Harzes – wodurch die Widerstandsfähigkeit der mehrschichtigen Leiterplatte gegenüber ESD-Ausfällen gestärkt wird.

5. Erweiterte Prozesse und Qualitätsprüfung

Da sich elektronische Geräte in Richtung Hochfrequenz und hoher Dichte entwickeln, Der ESD-Schutz steht vor neuen Herausforderungen und erfordert fortschrittlichere Prozesslösungen.

5.1 Prozessverbesserungen für spezielle Anwendungen

- Hochfrequenzkommunikationsszenarien: Low-Dk-Prepreg (Dk=3,48±0,03, Df<0,004) kann die Anforderungen an die 28-GHz-/77-GHz-Signalübertragung erfüllen und gleichzeitig einen zuverlässigen Isolationsschutz bieten – entscheidend für die Aufrechterhaltung der Signalintegrität und ESD-Beständigkeit in 5G- oder Automotive-Radar-Leiterplatten.

- Dicke Kupferplatten (≥3oz): Einführung einer „doppelschichtigen Prepreg-Laminierung mit niedrigem Harzgehalt“ (52%±1 % pro Schicht, Gesamtharzgehalt 56%) kombiniert mit 8MPa Hochdrucklaminierung. Dadurch kann die Durchbruchspannungsfestigkeit der dielektrischen Schicht auf 3500 V erhöht werden, was den ESD-Schutz für leistungsbezogene Leiterplatten verbessert.

- HDI (Hochdichte Interconnect) Bretter: Erfordert Prepreg mit geringer Fließfähigkeit (18±2mm) + Vakuumlaminierung, um das Problem des Harzüberlaufs bei 0,075 mm Mikrovia zu lösen. Diese speziellen Prozessbehandlungen verbessern nicht nur die Produktleistung, sondern erhöhen auch die interne ESD-Schutzfähigkeit der Leiterplatte.

5.2 Qualitätsverifizierungs- und Teststandards

Ein geschlossenes Qualitätsverifizierungssystem ist von entscheidender Bedeutung für die Gewährleistung der ESD-Schutzfähigkeit von Leiterplatten. Es beinhaltet:

- Eingehende Inspektion: Verwenden Sie Infrarotspektrometer, um den Gehalt an flüchtigen Stoffen zu testen, und dielektrische Spektrometer, um die Dk/Df-Stabilität zu überprüfen.

- Prozessüberwachung: Erfassen Sie während der Laminierung Temperatur- und Druckdaten in Echtzeit.

- Überprüfung des fertigen Produkts: Führen Sie Prüfungen der Zwischenschicht-Schälfestigkeit und des Isolationswiderstands durch.

Die abschließende ESD-Schutzprüfung muss den Anforderungen genügen IEC61000-4-2-Ebene 4 Standard, d.h., Prüfung der Kontaktentladung bis zu ±8 kV und Luftentladung bis zu ±15 kV. Nach dem Testen, Die folgenden Kriterien müssen erfüllt sein:

- Signalintegrität (Augendiagramm-Öffnung >70%).

- Bitfehlerrate (<1×10^-12).

- Betriebsstromschwankung (<± 5%).

- Zeiten zurücksetzen (0 Zeiten/Testzyklus).

Die heutigen Prozesse zur Chipherstellung werden immer ausgefeilter, Dies bedeutet jedoch nicht, dass wir unsere Wachsamkeit gegenüber ESD verringern können. Im Gegenteil, wenn die Schaltkreisgrößen schrumpfen und die Betriebsspannungen sinken, Bauteile werden empfindlicher gegenüber elektrostatischer Entladung.

Die heutigen Prozesse zur Chipherstellung werden immer ausgefeilter, Dies bedeutet jedoch nicht, dass wir unsere Wachsamkeit gegenüber ESD verringern können. Im Gegenteil, wenn die Schaltkreisgrößen schrumpfen und die Betriebsspannungen sinken, Bauteile werden empfindlicher gegenüber elektrostatischer Entladung.Hervorragende PCB-Ingenieure berücksichtigen den ESD-Schutz bereits in der ersten Entwurfsphase, Schutzmaßnahmen in die „DNA“ des Produkts integrieren. Dies ist nicht nur eine technische Herausforderung, sondern auch ein Test für Verantwortung und Professionalität – denn die beste Fehlerbeseitigung besteht darin, Fehler von vornherein zu verhindern.

UGPCB-LOGO

UGPCB-LOGO