Introduction: La guerre à l'échelle des millimètres dans la conception DDR5 PCB

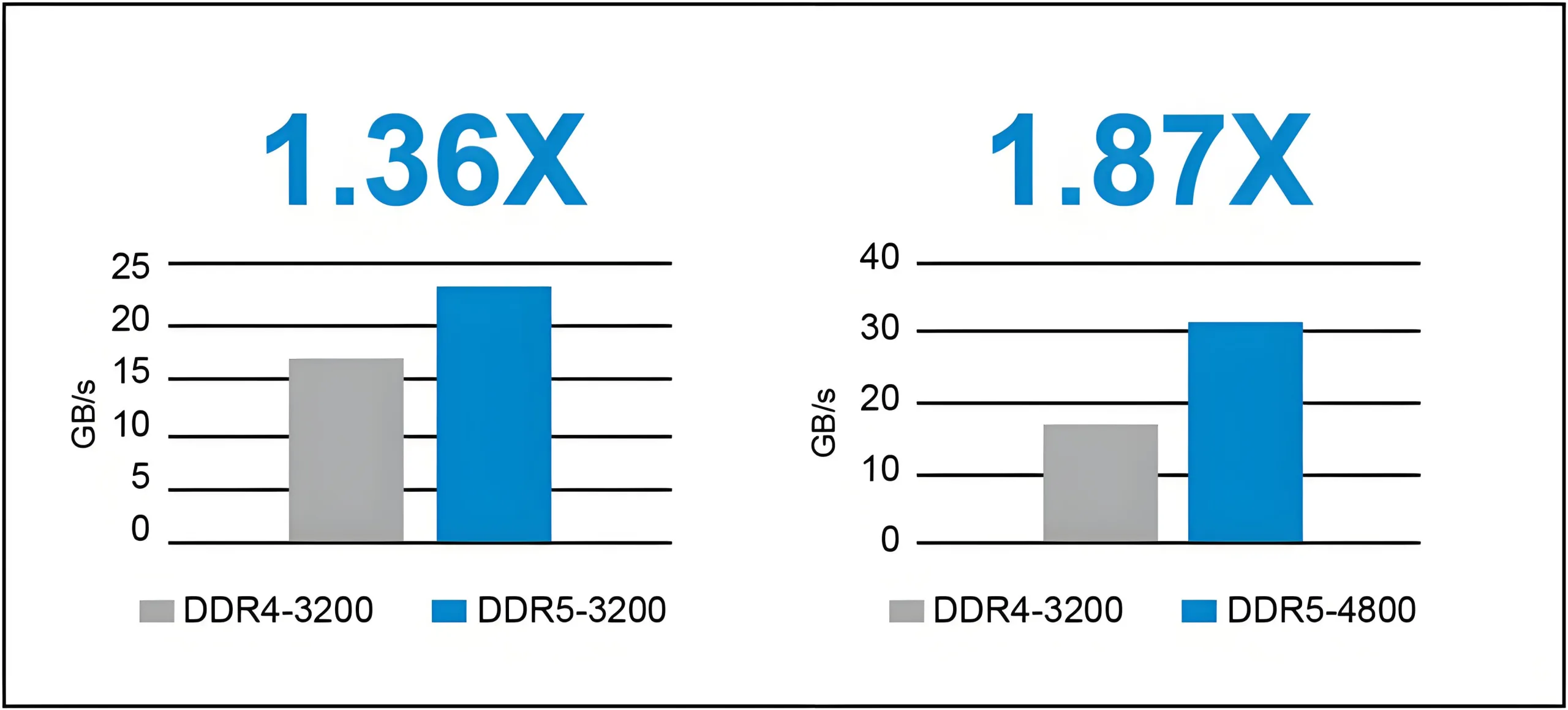

Le saut de DDR4 à DDR5 marque un changement de paradigme: Les taux de signal s'élèvent de 3,200 Mt / s à 6,400 MT / S pendant que les tensions de fonctionnement chutent à 1,1 V. Ce double défi se transforme PCB Routage de l'ingénierie de connectivité simple à la guerre de précision à l'échelle millimétrique. Les données de l'industrie révèlent que 80% des échecs de conception DDR5 proviennent des problèmes de routage, avec 90% évitable par simulation avant la couche. Cet article dissèque cinq pièges de routage DDR5 critiques, Soutenu par des données empiriques et des études de cas, Fournir des solutions exploitables pour les professionnels des PCB.

1. Caractéristiques physiques DDR5: Pourquoi les méthodes de conception des PCB traditionnelles échouent

1.1 Taux de signal et révolution de la bande passante

Pour DDR5-6400, La fréquence d'horloge efficace atteint 3,200 MHz, avec des taux de bord aussi vite que 0.5 ps (20-80% temps de hausse). Cela se déclenche:

-

Effet de la peau aggravée: Les courants à haute fréquence se concentrent sur les surfaces du conducteur, réduisant l'épaisseur efficace du cuivre à 0.66 μm à 10 GHz.

-

Escalade des pertes diélectriques: Substrats FR4 Présenter une perte tangente (Df) de 0.02 à 10 GHz, caution >3 DB / Inch-incedat atténuation.

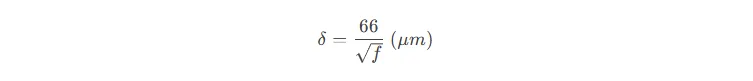

Validation de formule (Profondeur de la peau):

À F = 10 GHz, Δ≈0,66 μm,quitter le cuivre traditionnel de 1 oz (35 µm) avec <2% utilisation.

2. Cinq champs de mines de routage DDR5 et contre-mesures

2.1 Champ de mines 1: Erreur de synchronisation - le seuil de survie ± 15ps

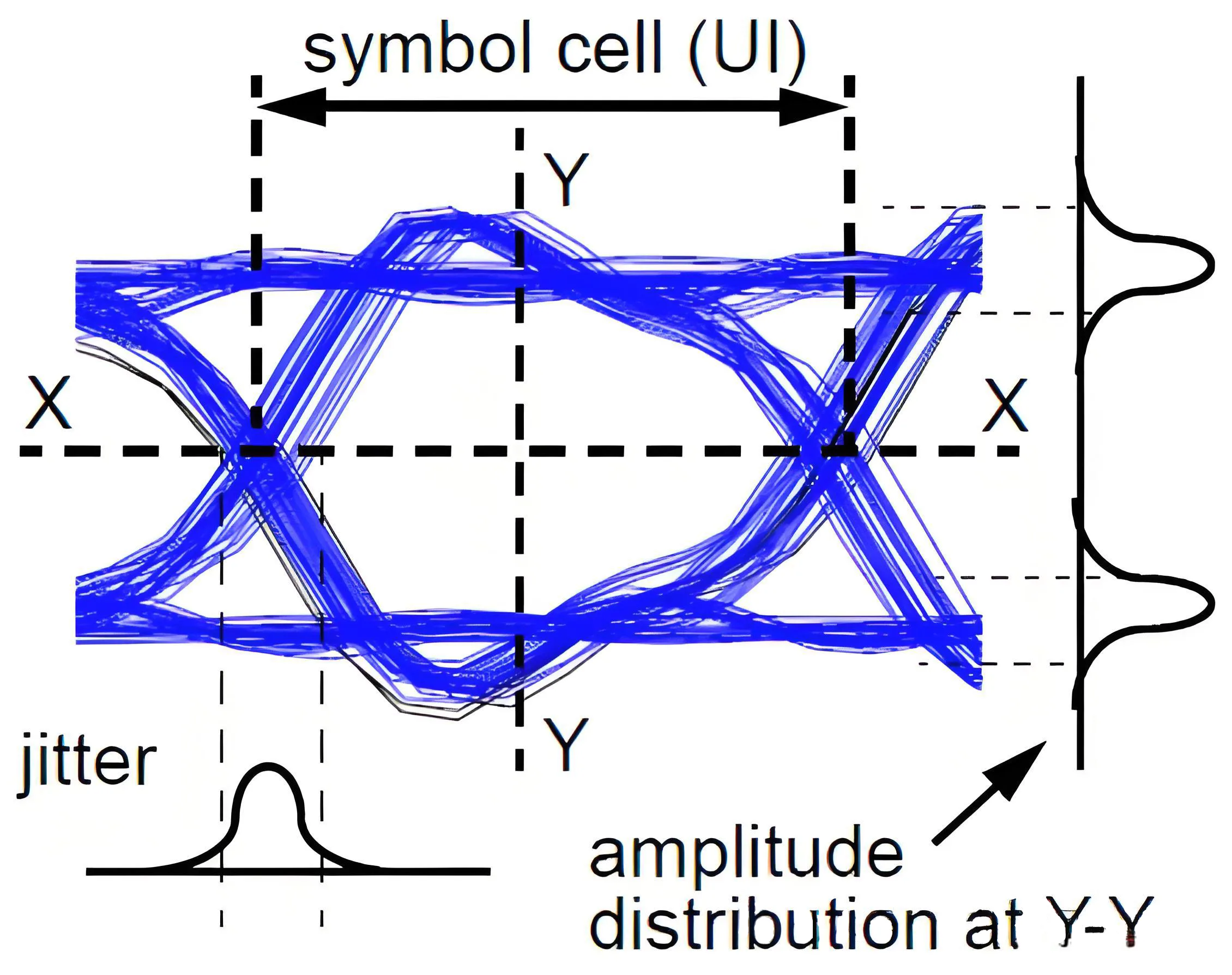

Impact: Un décalage de 5 mil de longueur introduit un délai de ± 12ps, s'effondrer la largeur des yeux horizontale par 30%.

Étude de cas: Une conception GPU a subi une dégradation de BER de 10−12 à 10−7 En raison de la biais de 8 mil DQ / DQS.

Solutions:

-

3D Compensation de routage: Remplacez les serpentines de 90 ° par des serpentines 45 °, réduisant la capacité parasite par 30%.

-

Étalonnage de synchronisation dynamique: Effectuer des simulations Monte Carlo (Cadence Sigrity) couvrant ± 10% des variations de processus.

Formule (Marge de synchronisation):

Tmarge= Tfaire du vélo-(Tco+Tvol+TGiron)

Pour DDR5-6400 (Tfaire du vélo= 0,3125 ), Les alertes du système déclenchent lorsque Tmarge<50 ps.

2.2 Champ de mines 2: Discontinuité d'impédance - le tsunami du signal 5Ω

Risque: Via des causes de décalage d'impédance >15 Perte de retour DB, s'effondrer la hauteur des yeux verticaux par 40%.

Données: Chacun non optimisé via 0.2 Perte d'insertion DB @ 5 GHz.

Solutions:

-

Via la révolution: Implémenter les vias laser-aveugles (≤4mil) avec compensation antipad, limiter la variation d'impédance à ± 3Ω.

-

Optimisation des pads: Utiliser des coussinets elliptiques (1.5:1 rapport d'aspect) pour réduire les effets capacitifs par 20%.

Formule (Via le modèle d'impédance):

Zvia≈87ϵr⋅ln(5.98h /(0.8d1 + d2))

Où : épaisseur diélectrique, D1: par diamètre, : diamètre du tampon.

2.3 Champ de mines 3: Délai de couche transversale - l'effet papillon 0,1ps / mm

Effet de tissage de fibres: Variation constante diélectrique (Δϵr = 0,3) à partir de la périodicité des fibres de verre 0.6 ps / pouces de retard.

Solutions:

-

Alignement de l'axe Z: Signaux de groupe d'octets d'itinéraire à des angles de ± 45 ° pour annuler l'anisotropie diélectrique.

-

Compensation entre la couche transversale: Préchargement de données DK / DF substrat dans les outils EDA pour la correction de retard automatique.

2.4 Champ de mines 4: Power Ripple - La réaction en chaîne nucléaire de 1 mV

Sensibilité: 50MV Ripple à 1,1 V L'offre augmente la gigue du conducteur par 20%.

Simulation: L'impédance cible PDN doit être ≤2 MΩ à 100 MHz - 5x plus strictes que les conceptions traditionnelles.

Solutions:

-

3D Matrice du condensateur: Déploier 0,1 μF (0402) + 10NF (0201) condensateurs près des circuits intégrés, revêtement 10 KHZ - 2 GHz.

-

Piliers de micro-cuivre: Intégrer des piliers de 200 μm de diamètre sous BGAS, Inductance de boucle de coupe par 30%.

2.5 Champ de mines 5: Perturbation du chemin de retour - La bombe EMI invisible

Risque EMI: Les plans de référence cassés génèrent un bruit de mode commun, dépassant les limites EMI par 10 db.

Solutions:

-

Coutures à la terre: Placer les vias au sol (≤0,1o) chaque 100 mil entre les couches de signal.

-

Pontage de places divisées: Utiliser des condensateurs enterrés (par ex., AVX 0402B) pour le couplage 10NF à travers les divisions de puissance.

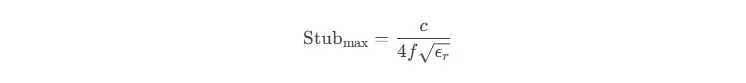

3. DDR5 Design Golden Rules: Formules et chaînes d'outils

3.1 Par limitation de talon:Pour DDR5-6400 (F = 3,2 GHz) sur FR4: Boutmax≤14,7 mm.

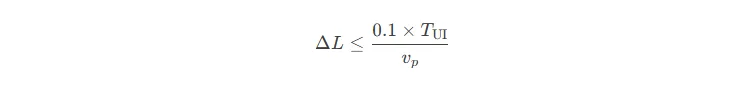

3.2 Tolérance différentielle à la paire:

Avec TUi= 0,3125 ns et Vp= 6 pouces /: Δl≤1,9 mil.

3.3 Cible d'impédance PDN:

Pour l'ondulation de 50 mV et le courant transitoire 10A: Zcible≤5 MΩ.

4. Réingénierie du processus de conception des PCB: De l'essai et de l'erreur à la simulation

4.1 Planification de la topologie:

-

Modèle vias dans HFSS; Optimiser les dimensions antipades.

-

Extraire l'impédance d'empilement via Siwave; Construire des bibliothèques S-Paramètre.

4.2 Exécution de routage:

-

Activer les chèques d'impédance en temps réel dans Allegro; violations de drapeau automatique.

-

Mettre en œuvre une topologie à vol avec un biais intra-groupe ≤ 2 mil.

4.3 Validation:

-

Effectuer des tests de diagramme oculaire (Annonces de Keysight) avec ≥ 70 mV de hauteur d'œil.

-

Mesurer les courbes TDR; Limiter la variation d'impédance à ± 5%.

Conclusion: Le “À trois corps” Loi de la conception DDR5

Sous la vitesse GHZ, millivolt-noise, et des contraintes de tolérance à micron, La conception de PCB DDR5 entre dans un “mécanique quantique” ère. Victoire dans l'intégrité du signal La guerre exige la convergence de la science matérielle (Substrats à faible DK), processus avancés (MSAP), et maîtrise de la simulation.

LOGO UGPCB

LOGO UGPCB