Tehnica tăierii unităților individuale de la napolitane și apoi ambalarea acestora a fost mult timp norma pentru ambalarea circuitelor integrate cu semiconductor de zeci de ani. Cu toate acestea, această abordare nu este în prezent adoptată de marii producători de semiconductori din cauza costurilor ridicate de producție și a componentei RF în creștere a modulelor de astăzi.. Astfel, apariția ambalajelor la nivel de napolitană (WLP) a condus la o schimbare de paradigmă în dezvoltarea ambalajelor la preț redus. WLP este o tehnologie de ambalare la nivel de napolitană înainte de tăierea dispozitivelor de ambalare a napolitanelor.

Folosind instrumente și procese standard, WLP acționează ca o extensie a procesului de fabricare a plachetelor. În cele din urmă, matrița WLP fabricată va avea un tampon metalizat pe suprafața cipului și un punct de lipit depus pe fiecare tampon înainte de a tăia napolitana. Acest, la rândul său,, face WLP compatibil cu procesele tradiționale de asamblare PCB și permite testarea dispozitivului pe wafer în sine. Ca urmare, este un proces relativ redus și eficient, mai ales pe măsură ce dimensiunea plachetei crește și chipul DIE se micșorează. Dimensiunea napolitanelor a crescut în ultimele decenii, din 4, 6, şi 8 inci în diametru până la 12 inci. Acest lucru are ca rezultat o creștere a numărului de DIE per plachetă, ceea ce scade costurile de fabricatie. În ceea ce privește performanța electrică, WLP este superior altor tehnologii de ambalare, în sensul că odată ce un dispozitiv WLP este integrat într-un modul RF dens, are ca rezultat o reducere semnificativă a cuplării parazitare EM, deoarece interconectarea dintre dispozitiv și PCB este relativ scurtă, spre deosebire de interconexiunea legată de sârmă utilizată în unele tipuri de tehnologii CSP.

Tehnologia flip-chip cu cip WLP

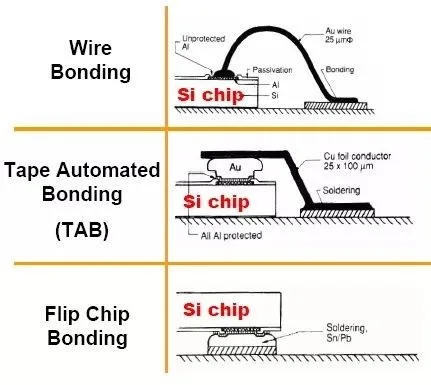

Tehnologia Flip-Chip, cunoscută și sub numele de Conexiune Controlled Collapse Chip (C4), este una dintre numeroasele tehnologii de asamblare a cipurilor dezvoltate de IBM în anii 1960. Deși tehnologia de ambalare bazată pe lipirea firelor este mai flexibilă în ceea ce privește capacitatea inductivă gratuită pentru depanarea în laborator după ce hardware-ul este construit, și oferă, de asemenea, o bună conductivitate termică, utilizarea umflăturilor de lipire în tehnologia de ambalare flip-chip face ca conexiunea electrică dintre substratul pachetului și cip să ofere o reducere relativă a dimensiunii, latență redusă, și o mai bună izolare în ceea ce privește pinii de intrare și de ieșire. Figura 1 ilustrează structura de bază a chipului DIE pe substrat, cu o bilă de lipit în vârful coloanei de Cu care crește pe suprafața așchii. Îmbinarea de lipit este de obicei încapsulată cu un compus de matriță de umplutură pentru a oferi suport mecanic pentru îmbinarea de lipit.

Tehnologia flip-chip cu cip WLP

Pachet la nivel de cip WLP

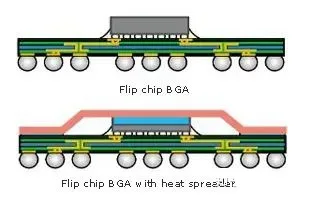

Ambalare cu scară de așchii (CSP) este una dintre cele mai utilizate metode de ambalare în industria microelectronică și semiconductoare. În timp ce mai multe tipuri de tehnologii CSP sunt deja disponibile pentru producătorii de microcipuri, continuă să apară noi tipuri pentru a satisface cererea de produse care acceptă noi funcții și noi produse specifice aplicațiilor. Aceste cerințe de ambalare pot varia în funcție de nivelul necesar de fiabilitate, cost, caracteristici suplimentare, și dimensiunea totală. După cum sugerează și numele, dimensiunea pachetului CSP este aproximativ aceeași cu dimensiunea chipului DIE, care este unul dintre principalele sale avantaje. Prin adoptarea procesului de fabricație WLP, CSP este dezvoltat în mod constant pentru a obține cel mai mic raport posibil de dimensiune pachet-matrice. După cum se arată în figura 2, matricea grilă bile (BGA) stilul CSP din pachet permite mai multe interconexiuni, simplificând în același timp cablarea PCB, creșterea debitului de ansamblu PCB și reducerea costurilor de producție.

Ambalare la nivel de napolitană

Alte tehnologii de încapsulare

Există mai multe alte forme de ambalare IC integrată care permit integrarea perfectă în pachete de module personalizate pentru aplicație. Pachet plat Quad (MFF) este una dintre cele mai vechi tehnologii de pachet IC cu montare la suprafață,unde structura pachetului este compusă din patru laturi cu cabluri de interconectare extinse, după cum se arată în figura 3(o). Cablurile ridicate sunt conectate la cadrul pachetului pentru a forma un metal-izolant-metal (MIM) tip condensator între cabluri și cipul DIE metal, care poate fi folosit ca element de potrivire. Această tehnică este potrivită pentru circuitele integrate de dimensiuni milimetrice în care numărul de pini periferici din pachet poate atinge mai mult de 100 pini. Există mai multe derivate ale acestui tip de încapsulare, in functie de materialul folosit, cum ar fi pachetul plat quad ceramic, pachet subțire quad plat, pachet plat quad din plastic, Pachet plat din plastic Quad) și Metal Quad Flat Pack (MQFP). QFN-ul, Quad Flat fără plumb, prezentat în Fig. 3(b) este una dintre mai multe tehnologii de ambalare montate pe suprafață formate dintr-un cadru plat de plumb de cupru și un pachet de plastic folosit ca suport de transfer de căldură pentru radiator. Lipirea firelor poate fi folosită și pentru interconexiuni, și deoarece liniile de legătură nu sunt numai conductoare, ci și inductori, ele afectează în general performanța dispozitivelor în cadrul acestei tehnici de încapsulare, cu excepția cazului în care este considerat ca parte a proiectului general. Deși QFN este o interconectare formată din patru părți, biplanul unled conduce (DFN) au apărut și formează ambele părți ale cablurilor planului de interconectare.

LOGO UGPCB

LOGO UGPCB