Введение: Файлы Gerber - ДНК производства печатной платы

В Высокоскоростной дизайн печатной платы, Файлы Гербера инкапсулируют 90% производственных данных. Согласно стандартам IPC-2581, 85% глобального Производители печатной платы Полагаться на Гербер в качестве первичной производственной документации. Как “Промышленный план” электроники, Файлы Гербера точно описывают физическую структуру платы через многослойную кодировку. Это руководство декодирует инженерное значение каждого уровня, чтобы помочь вам освоить Изготовление печатной платы.

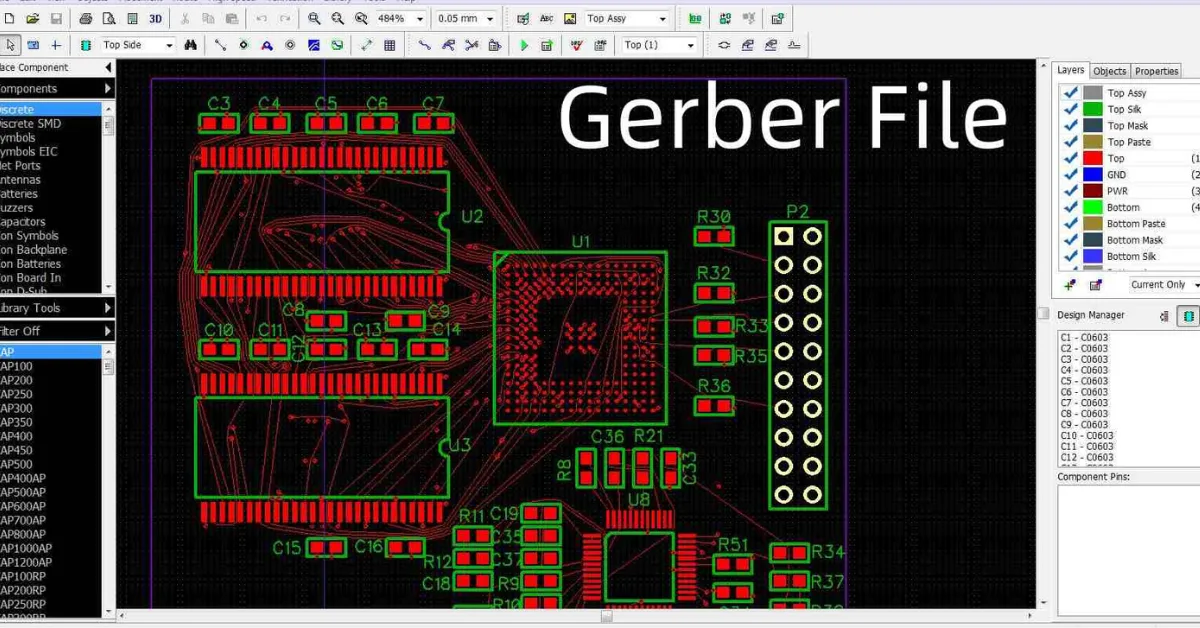

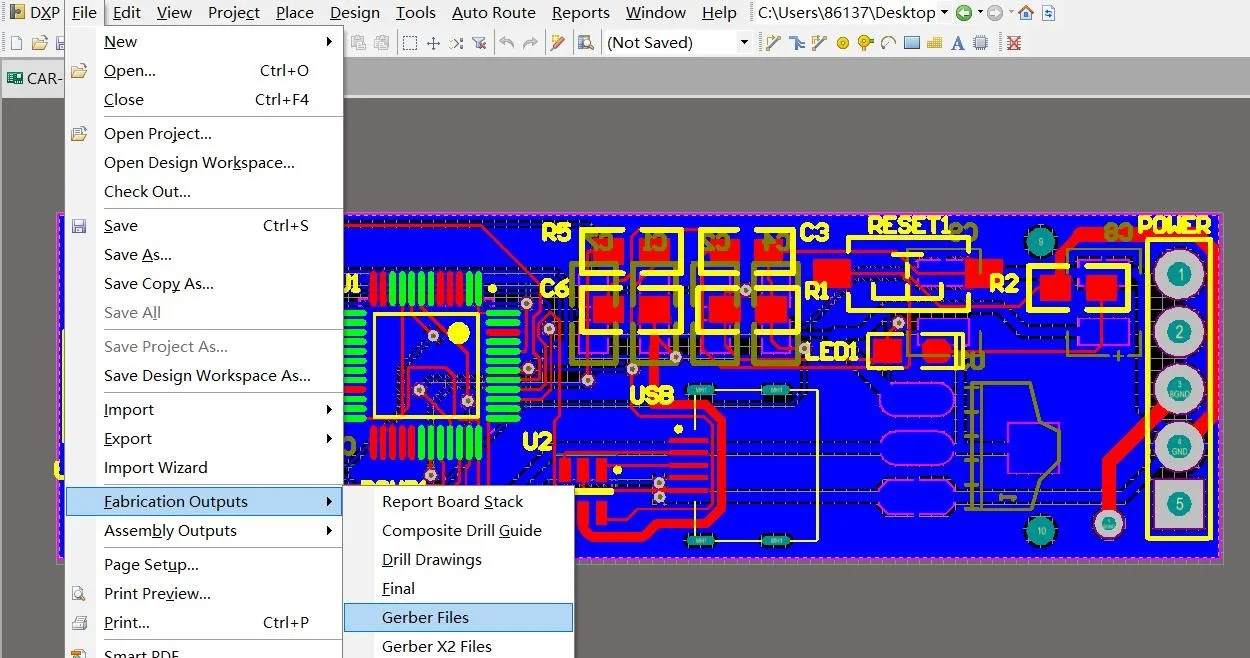

Раздел 1: Завершите рабочий процесс экспорта файла Gerber

1.1 Предварительная экспортная проверка

-

Validation DRC: Обеспечьте соответствие между стандартами IPC-2221 IPC-2221 (Мин. трассировка/пространство = 0,1 мм при 6-слойном печатные платы)

-

Подтверждение Stackup: Контроль импеданса должен удовлетворять:

Где ЧАС = диэлектрическая толщина, Вт = ширина трассировки, Т = толщина меди (1 Оз = 35 мкм).

1.2 Сравнение режима экспорта

| Метод | Вариант использования | Файл полноты |

|---|---|---|

| Экспорт одного клика | Стандартный 4-6 СЛОВАЯ ПХБ | 95% |

| Пользовательская конфигурация | HDI PCBS / Слепые/похороненные вайи | 100% |

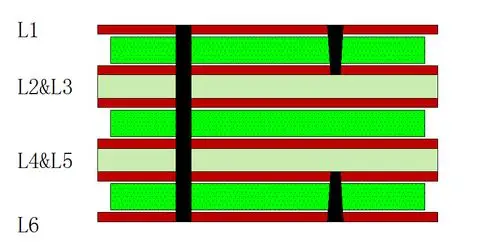

Раздел 2: Структура слоя Гербера глубокое погружение

2.1 Проводящие слои объяснены

Медные слои:

-

Верхний/нижний слой: Поверхностная маршрутизация (Тип. 1 Оз меди)

-

Внутренние слои: 6-слой PCB Stackup: Top-Gnd-Signal-Power-Signal-Bottom

Буровые слои:

2.2 Слои поддержки процесса

Слоя припоя маски:

-

Отрицательный вывод изображения (Разоблачает медные отверстия)

-

Мин. прозрачный: 0.07мм (Предотвращает провал мостики паяльной маски)

Вставьте слой маски:

-

Апертура трафарета = размер прокладки × 90%

-

Пакеты QFN требуют конструкции боевых бусинок поперечного моста

Шелкостный слой:

-

Высота текста ≥0,8 мм, ширина линии ≥0,15 мм

-

Нижний слой шелковидный экрану требует зеркалирования

Раздел 3: Гербер функционирует в многослойных печатных платах

3.1 Количество слоев против. Файлы Гербера

| Слои печатной платы | Файлы Гербера | Специальные требования |

|---|---|---|

| 1-2 | 8-10 | Стандартные сквозные отверстия |

| 4-6 | 15-20 | Контроль импеданса + Виппо |

| 8+ | 25+ | Слепые исчезновения + гибридная укладка |

3.2 Расширенная реализация процесса

Виппо (Via-in-Pad):

-

Диаметр отверстия ≤0,15 мм, Размер прокладки ≥0,3 мм

-

Метка как “μvia” в бурильных слоях

Stepped Slot Design:

-

Механикояллеяер:

SLOT:3.0x1.2mm @ Layer2-4

Раздел 4: Правила DFM, обусловленные данными Gerber

4.1 Проверка производительности

4.2 Высокоскоростные маркеры дизайна

-

Дифференциальные пары:

IMPEDANCE:100Ω±10% -

РФ следы:

NO_SOLDERMASK(Уменьшает вариации DK)

Раздел 5: От инженера макета до архитектора PCB

True PCBA Design Experts Master:

5.1 Целостность сигнала (И)

-

Контроль задержки: ΔL ≤ 0,05 адрес (пс/дюйм)

-

Профилактика перекрестных помех: 3W Правило (Расстояние ≥ 3 × ширина трассировки)

5.2 Целостность власти (ПИ)

-

Цель импеданс:

-

Развязка компоновки конденсатора: Радиальное размещение емкостью

5.3 Тепловое управление

-

Медный ток пропускной способности:

I = 0,048 OT0,44 A0,725

(ΔT = повышение температуры, A = поперечное сечение)

Заключение: Инженерная философия Gerber Files

При экспорте данных Гербера, помнить: Эти “холодный” Слои представляют собой точные диалоги между электроникой и материаловедением.. От 0,05 мм лазерных сверстников до 10 мкм допусков паяной маски, Каждый слой Гербера рассказывает инженерную философию выделения сигналов и проводящих путей.

Отраслевые данные показывают: Использование Gerber+ODB ++ Двойной доставки увеличивает выход первого прохождения 40%. В эпоху 5G/AI, Освоение семантики Гербера означает контроль ядра интеллектуального производства оборудования.

ЛОГОТИП УГКПБ

ЛОГОТИП УГКПБ

Вы на самом деле заставляете это выглядеть так легко вместе с вашей презентацией, однако я считаю, что эта тема действительно одна вещь, которую я чувствую, я ни в коем случае не пойму.

Это кажется слишком сложным и очень обширным для меня.

Я с нетерпением жду вашей последующей публикации, Я попытаюсь понять это!

Я любил столько, сколько вы получите прямо здесь.

Эскиз привлекателен, Ваш авторский предмет стильный.

тем не менее, Вы командоваете получить нетерпение к тому, что вы хотите доставить следующее.

Нездоровый, несомненно, появляется более ранее, так как точно так же очень часто внутри.

Вы защищаете это увеличение.