Dans le domaine de l'ingénierie électronique, le nombre de couches d'un Circuit imprimé (PCB) est souvent un indicateur direct de la complexité et de la sophistication technologique d’un produit. Alors que la plupart des ingénieurs travaillent régulièrement avec 2, 4, ou des cartes à 6 couches, l'électronique grand public utilisant même des solutions à coûts optimisés telles que “pseudo-8 couches” planches (6 couches électriques fonctionnelles plus 2 couches d'isolation pour l'épaisseur)— le paysage change radicalement dans les serveurs haut de gamme, cartes mères informatiques hautes performances, et des équipements de communication de pointe. Ici, PCB avec 16, 32, ou même 64 les couches sont communes. Cela soulève une question cruciale: quels sont les principes de conception sous-jacents et les technologies de fabrication qui permettent à ces PCB à nombre de couches élevé? Cet article fournit une analyse approfondie des aspects techniques, principaux défis, et des solutions de fabrication avancées pour les PCB à nombre de couches élevé.

Pourquoi des PCB à nombre de couches élevé? Plus qu'un simple jeu de routage

Augmenter le nombre de couches de PCB ne consiste pas à rechercher des chiffres impressionnants. Le moteur fondamental est la croissance exponentielle des exigences de performances des appareils électroniques modernes.. Quand la densité des broches de puce continue d'augmenter (par ex., Forfaits BGA avec plus 2500 billes de soudure), les vitesses des signaux entrent dans le régime GHz (par ex., Pie 5.0 à 32 GT/s), et les systèmes doivent gérer simultanément le numérique à haut débit, Analogique RF, et signaux haute puissance, traditionnel 4 ou les panneaux à 6 couches deviennent inadéquats.

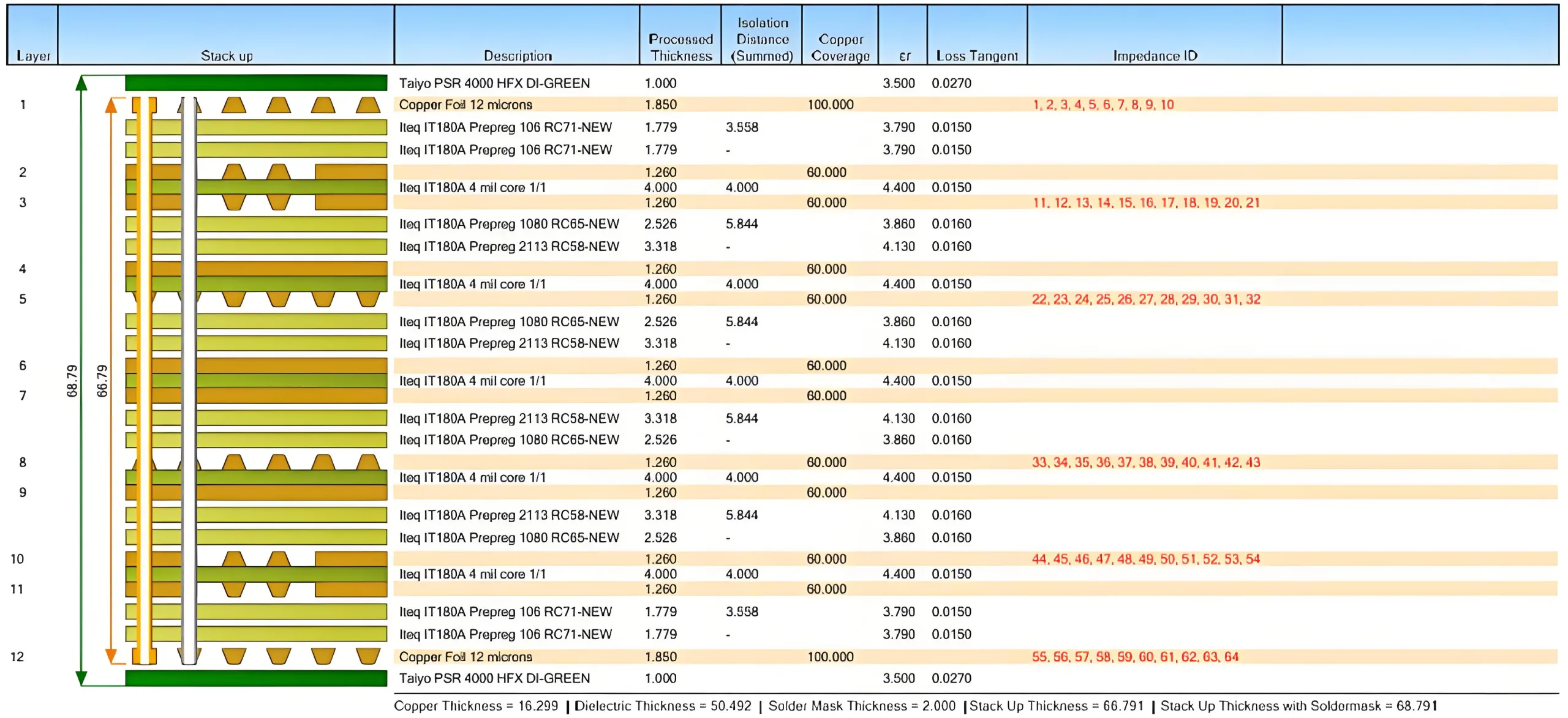

La valeur fondamentale des PCB à nombre de couches élevé réside dans la fourniture de ressources de routage suffisantes et de plans de référence complets.. Un empilement typique de cartes à 12 couches pourrait être: Signal 1 / Sol / Signal 2 / Pouvoir 1 / Signal 3 / Sol / Signal 4 / Pouvoir 2 / Signal 5 / Sol / Signal 6. Ce symétrique “signal-de-terre-puissance-signal-terre” empilement (suivre les directives comme IPC-2141A) contrôle efficacement l'impédance et fournit un chemin de retour à faible bruit pour les signaux à grande vitesse. Statistics show that in equipment like data center switches, designs using PCBs with 20+ layers can reduce crosstalk in critical network signals by over 60% (data referenced from IPC TR-579 report).

Design Challenges for High-Layer Count PCBs: Beyond “Drawing Traces”

Signal Integrity and Impedance Control

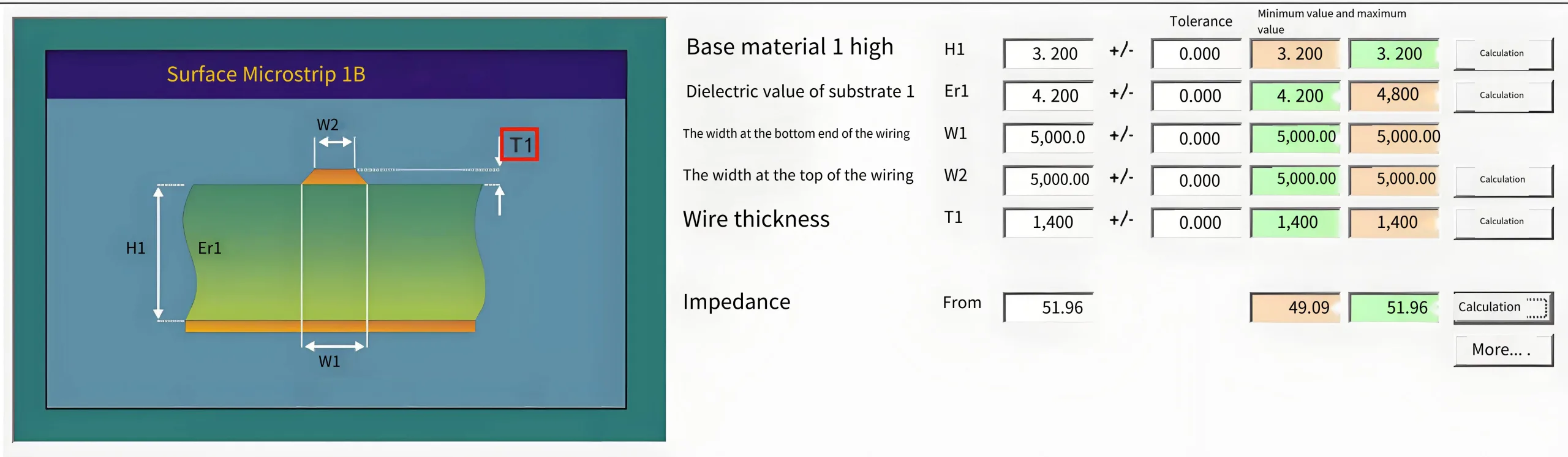

In high-speed design, PCB traces are no longer simple electrical connections but must be precisely controlled transmission lines. Deviations in characteristic impedance (par ex., 50Ω asymétrique, 90Ω/100Ω differential) directly cause signal reflection, overshoot, and data eye diagram closure. Impedance primarily depends on trace width (W), épaisseur diélectrique (H), constante diélectrique (εr), et épaisseur de cuivre. Industry-standard tools like Polar Si9000 model this using simplified formulas (pour les lignes microrubanques):

Z0 ≈ (87 / √(εr + 1.41)) * ln(5.98 * H / (0.8 * W + T))

where T is trace thickness. For common FR-4 material (εr ≈ 4.2 @ 1GHz), pour atteindre une impédance de 50Ω avec une épaisseur diélectrique H=5 mil, la largeur de trace W doit être contrôlée à environ 8.5 mil. Cependant, non-uniformité dans la structure laminée des panneaux à haute couche, l'effet de tissage de verre, et tolérances de gravure de production (généralement ±10 %) tous introduisent des variations d'impédance. La norme IPC-6012D autorise un écart de ± 10 % de la valeur mesurée par rapport à l'impédance nominale pour les cartes à impédance contrôlée, mais les applications haut de gamme exigent désormais des tolérances aussi strictes que ±7 %.

Intégrité de l’alimentation et gestion thermique des PCB

À mesure que le nombre de couches augmente, la complexité du réseau de distribution d'énergie (RPD) le design croît de façon exponentielle. Les tensions du noyau peuvent descendre jusqu'à 0,8 V avec des courants transitoires atteignant des centaines d'ampères.. Dans ce scénario, l'impédance cible des avions de puissance doit être extrêmement faible (par ex., <1 MΩ) pour supprimer l'ondulation de tension. Cela nécessite une planification minutieuse du placement des condensateurs de découplage., optimisation de la capacité inter-plans entre les plans d'alimentation et de masse (calculé par C = ε0 * εr * A / d, où A est la zone de chevauchement et d est l'épaisseur diélectrique), et peut nécessiter des couches de puissance dédiées. En outre, densité de puissance accrue grâce au routage haute densité (dépassement 100 W/cm² dans certaines zones ASIC) nécessite un refroidissement amélioré grâce à des baies thermiques, pièces de cuivre incorporées, ou substrats métalliques, ajoutant encore plus de complexité à la conception et au traitement de l'empilement.

L'alchimie de la fabrication de PCB: La chaîne de processus de précision pour les cartes à nombre de couches élevé

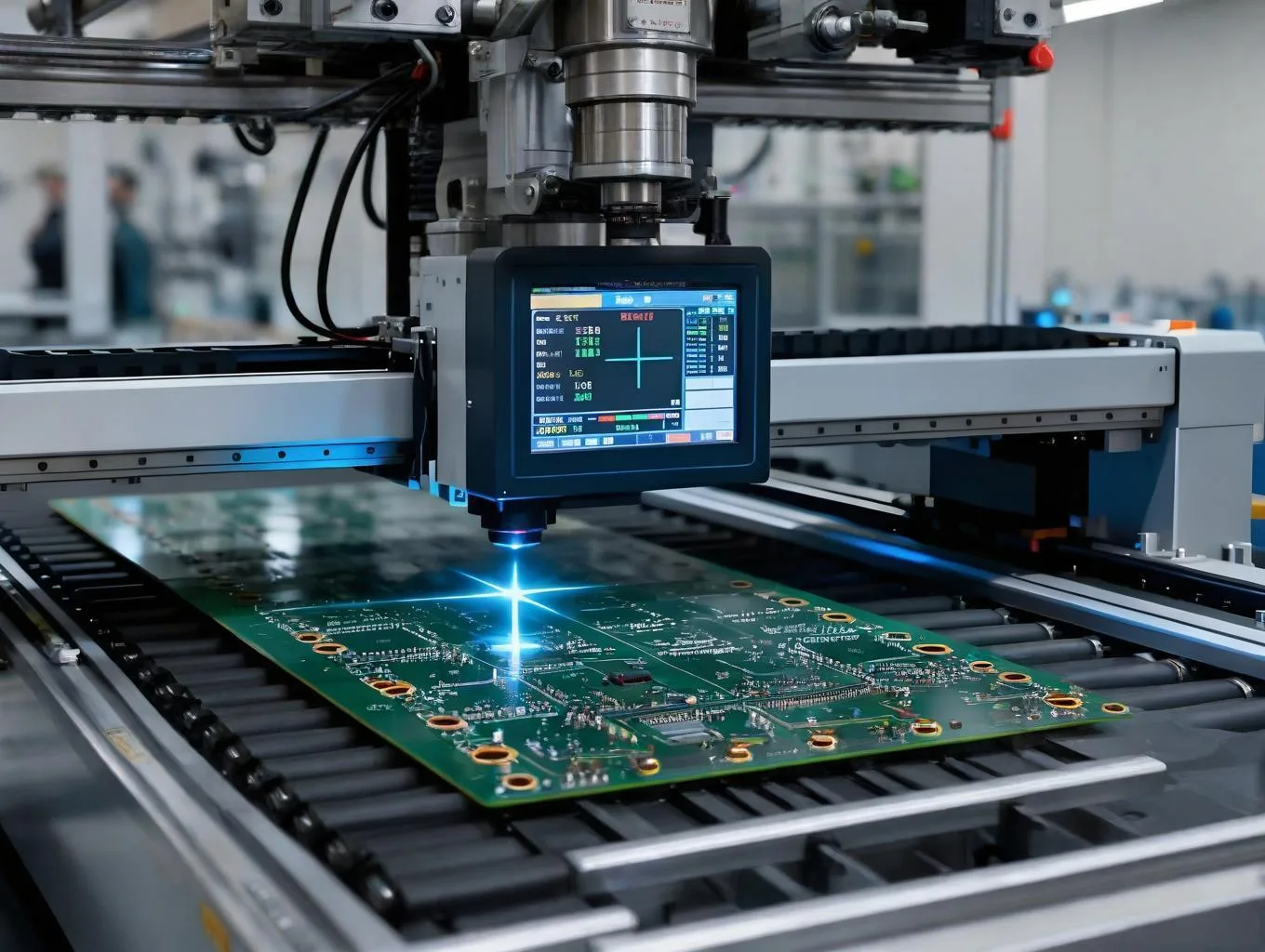

Transformer la conception en réalité physique présente un autre défi important pour les PCB à nombre de couches élevé. Le processus de base peut être résumé comme un cycle précis de “stratification – alignement – perçage – placage.”

Alignement couche à couche: L'art de l'enregistrement au niveau micronique

Toutes les couches d'un panneau multicouche (noyaux de couche intérieure et préimprégné) doit être laminé en une seule unité sous haute température et pression. Un mauvais repérage des couches peut entraîner la coupure des traces par les forets, créer des courts métrages, ou provoquer des discontinuités d'impédance. Pour une planche à 16 couches, si l'erreur d'alignement moyenne par couche est 25 µm (la tolérance d'enregistrement graphique autorisée par la classe IPC-A-600G 3), l'erreur cumulée dans le pire des cas pourrait dépasser 100 μm—suffisamment pour compromettre un 0.2 mm tampon BGA.

Des fabricants de premier plan comme l'UGPCB relèvent ce défi en utilisant Imagerie directe laser (ILD) et systèmes d'alignement optique de haute précision. Goupilles d'alignement et échelles fiduciaires mondiales gravé sur chaque couche centrale, combiné avec la capture de vision CCD et le réglage des servos, peut contrôler l'enregistrement de couche à couche dans 15 µm (données basées sur les livres blancs sur les processus des principaux fournisseurs du secteur). En plus, analyse de la rhéologie des matériaux pour prédire l'écoulement de la résine et l'orientation des fibres de verre du préimprégné pendant le laminage, permet une pré-compensation de la déformation dimensionnelle, assurant une épaisseur diélectrique uniforme après pressage.

https://example.com/pcb-lamination-alignment.png

Texte alternatif de l'image: Explication détaillée du processus de stratification et d'alignement des PCB multicouches, montrant des cibles laser, alignement optique, et flux de laminage, garantissant un enregistrement couche à couche de haute précision.

Via l'interconnexion: Des trous traversants au HDI n’importe quelle couche

Les trous traversants traditionnels pénètrent dans toute l'épaisseur du panneau, occupant un espace de routage important dans les PCB à nombre de couches élevé et provoquant de longs problèmes de chemin de retour du signal. Donc, Interconnexion à haute densité (IDH) technologie permet des transitions de calque plus flexibles en utilisant vias aveugles (de la surface à la couche intérieure), vias enterrés (couche intérieure à couche intérieure), et Microvias (diamètre ≤ 0.15 mm).

Par exemple, un “1+N + 1” Structure de l'IDH (où les couches de surface utilisent des microvias et le milieu est un noyau traditionnel à N couches) peut augmenter la densité de routage de plus de 40% sans augmenter le nombre total de couches (faisant référence à la norme de conception IPC-2226 HDI). Cependant, cela introduit des complexités de processus telles que perçage par stratification séquentielle, via le remplissage et le placage, et plusieurs cycles de stratification. Les constructeurs doivent équiper perceuses laser (pour microvias), machines de bouchage sous vide verticales (pour garantir un remplissage sans vide), et équipement de nettoyage au plasma (pour enlever les traces de forage), et effectuer rigoureusement test de sonde volante et test Kelvin à quatre fils vérifier la fiabilité de chaque point d’interconnexion.

Tendances futures: Innovation matérielle et intégration conception-fabrication basée sur la simulation

L'évolution des PCB à nombre de couches élevé se poursuit. À mesure que les débits de signal progressent vers 56 Gbit/s et au-delà grâce à la modulation PAM4, matériaux à faibles pertes (comme Panasonic MEGTRON 6, Série Rogers Ro4000) avec εr aussi bas que 3.2 et facteurs de dissipation (Df) ci-dessous 0.002 sont en cours d'adoption. Simultanément, composants embarqués (comme les résistances et les condensateurs enterrés) et intégration de packages de semi-conducteurs (par ex., L'EMIB d'Intel, SoIC de TSMC) brouillent les frontières entre les PCB et les CI.

Pour les concepteurs et les spécialistes des achats, sélectionner un qualifié nombre de couches élevées Fournisseur de PCB est primordial. Au-delà de se concentrer sur leur capacité de couche maximale (par ex., production de masse stable de 32 couches), contrôle d'impédance capacité (s'ils fournissent des rapports de tests d'impédance), et Niveau du processus IDH (taille minimale du trou/largeur de trace), il est crucial d'évaluer leur services d'aide à la conception (tels que la simulation SI/PI et les conseils d'optimisation du stack-up) et système de contrôle de qualité (respect de la classe IPC 3 normes et disponibilité d’équipements d’inspection complets comme AOI, AVI, 3D radiographie).

À la recherche d'une haute fiabilité, haute performance carte PCB multicouche solution? Contacter un fournisseur professionnel doté de capacités complètes, de la simulation de conception à la fabrication de précision, pour obtenir un proposition de conception de stack-up personnalisée et devis instantané pour votre projet est la première étape critique vers le succès. À l’ère de l’Internet des Objets et de l’explosion informatique, les PCB à nombre de couches élevé ne sont plus de simples supports; ils constituent la pierre angulaire fondamentale définissant les limites de performance des systèmes électroniques.

LOGO UGPCB

LOGO UGPCB

Je ne sais pas où vous obtenez vos informations, mais super sujet. J'ai besoin de passer du temps à en apprendre davantage ou à mieux comprendre. Merci pour ces merveilleuses informations. Je cherchais ces informations pour ma mission.