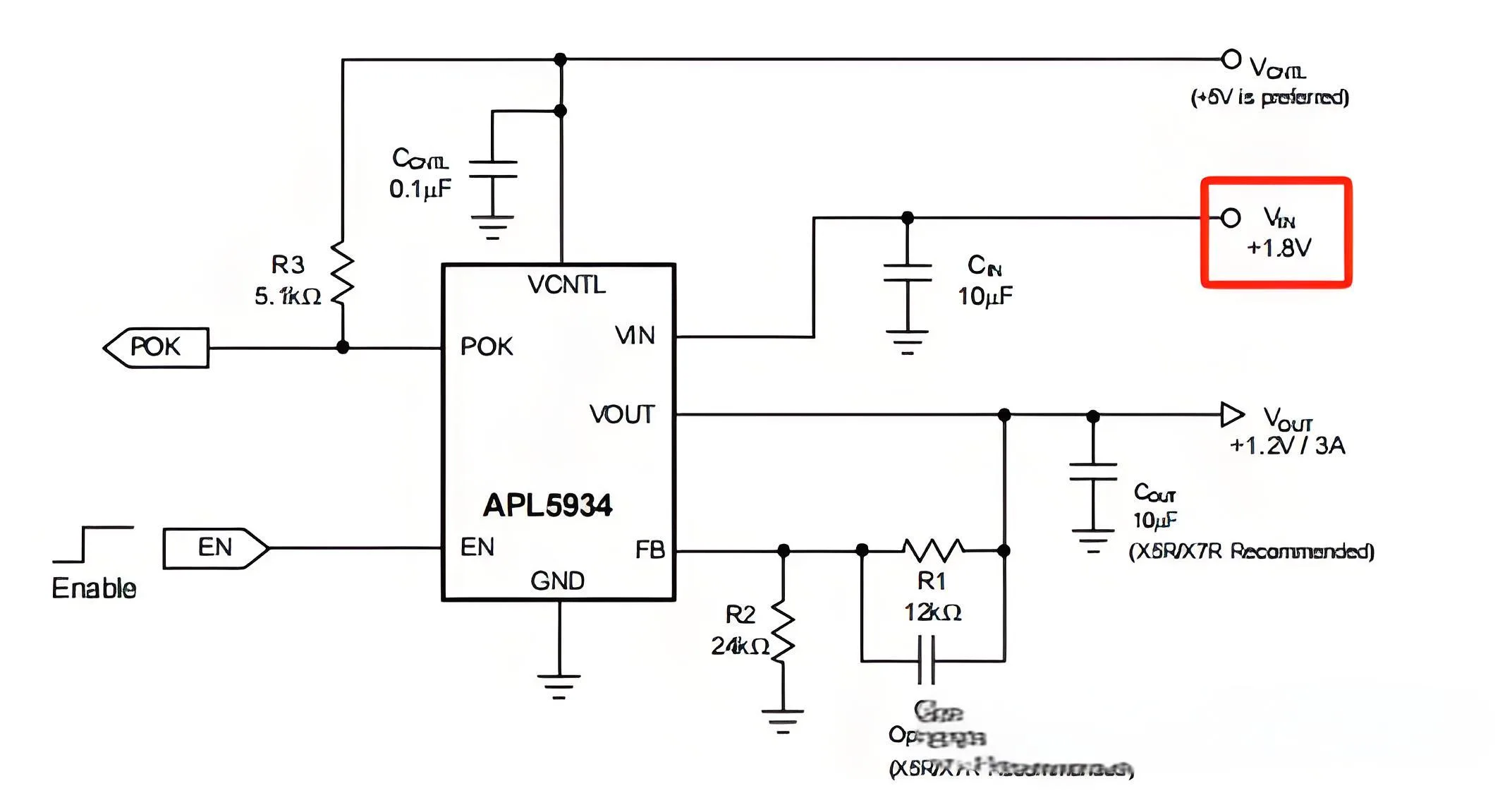

Dans le processus de l'ensemble de montage de surface PCBA, Divers composants électroniques échouent souvent. Aujourd'hui, Nous partageons une étude de cas sur l'analyse des échecs d'un régulateur linéaire 3A, expliquer comment regarder au-delà de la surface et identifier rapidement la faille.

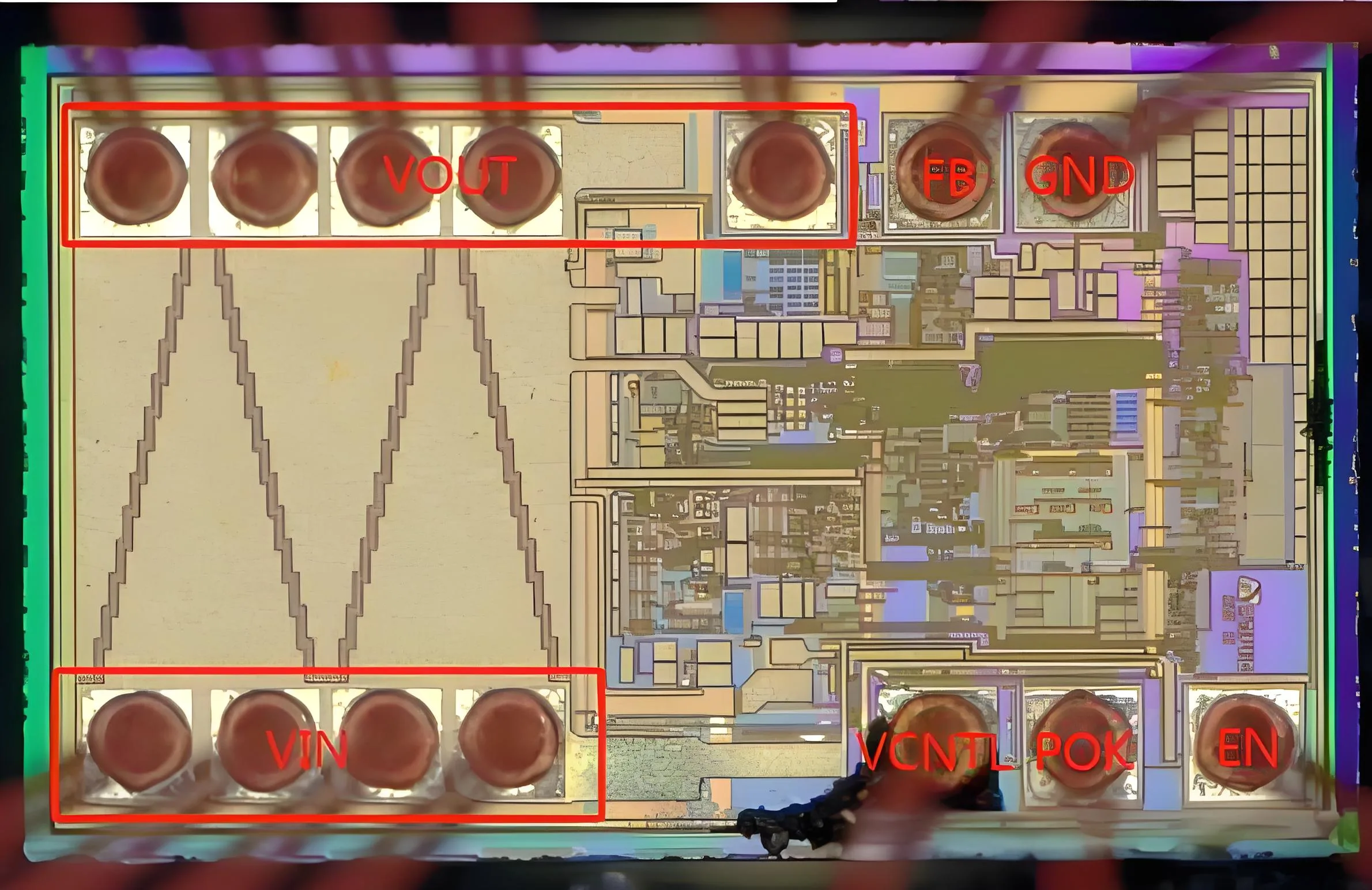

1) Description de l'échec de la puce: Vin est court-circuit au sol.

Vin est court-circuit au sol.

2) Analyse de l'échec de l'appareil: La puce a connu un EOS (Stressaire électrique) Échec comme confirmé par les tests IV avec le VIN court-circuit au sol.

Le test IV confirme VIN à court-circuit au sol.

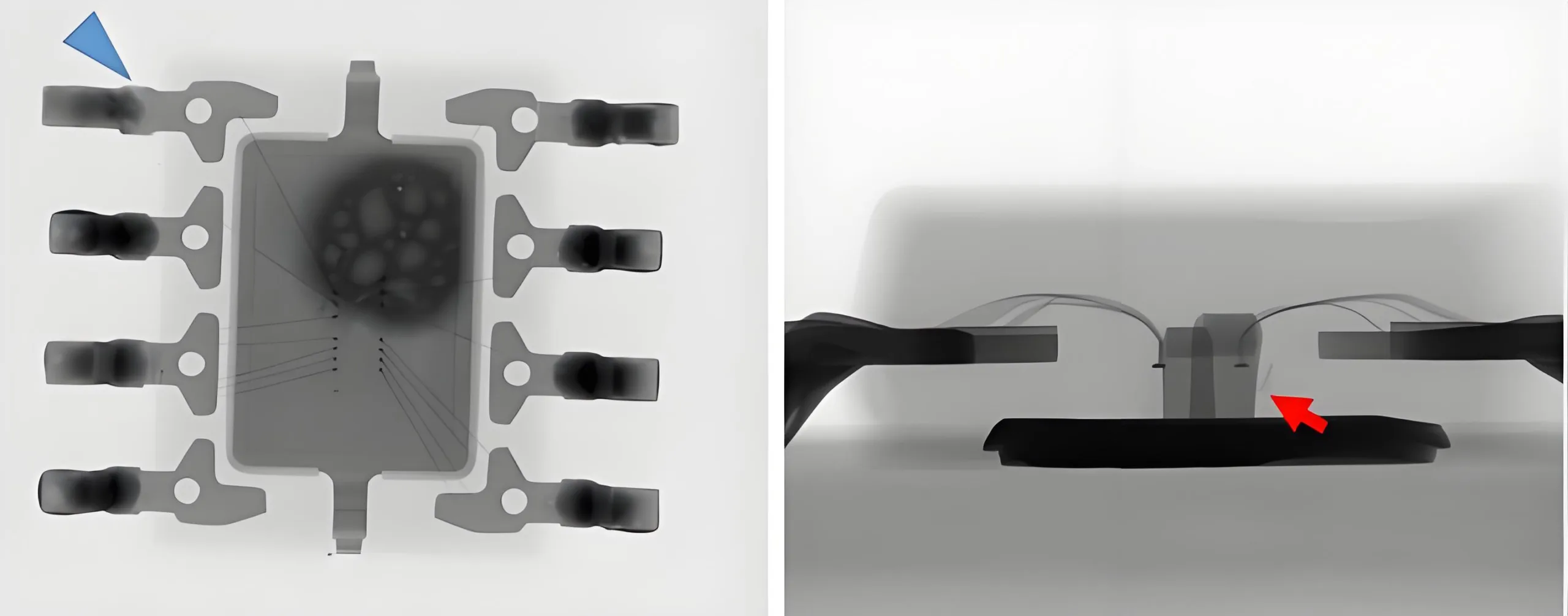

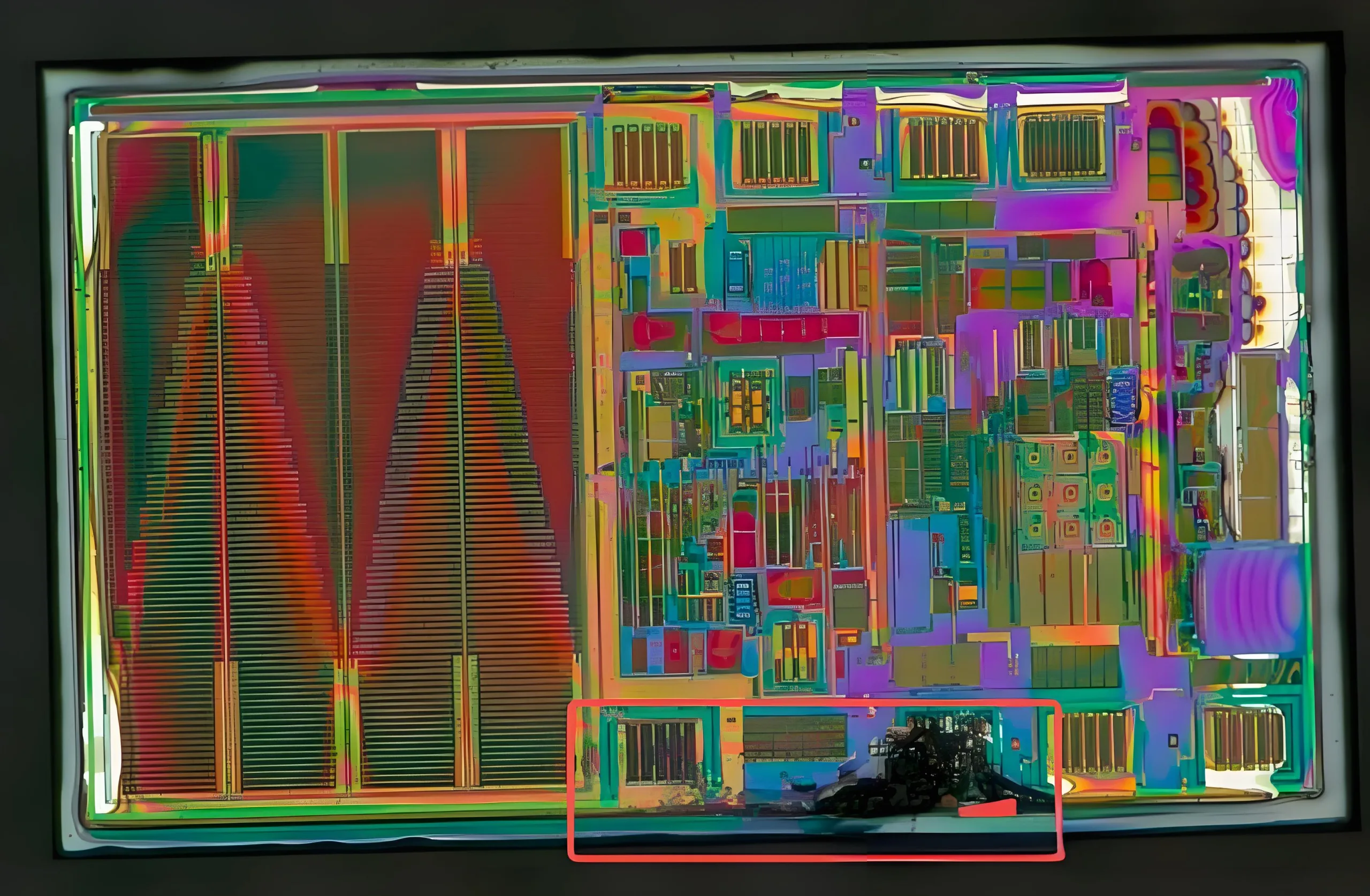

Aucune anomalie évidente n'a été observée en apparence ou en balayage acoustique, Mais la radiographie a révélé des dégâts de brûlure suspectés.

Soupçonné d'avoir été brûlé

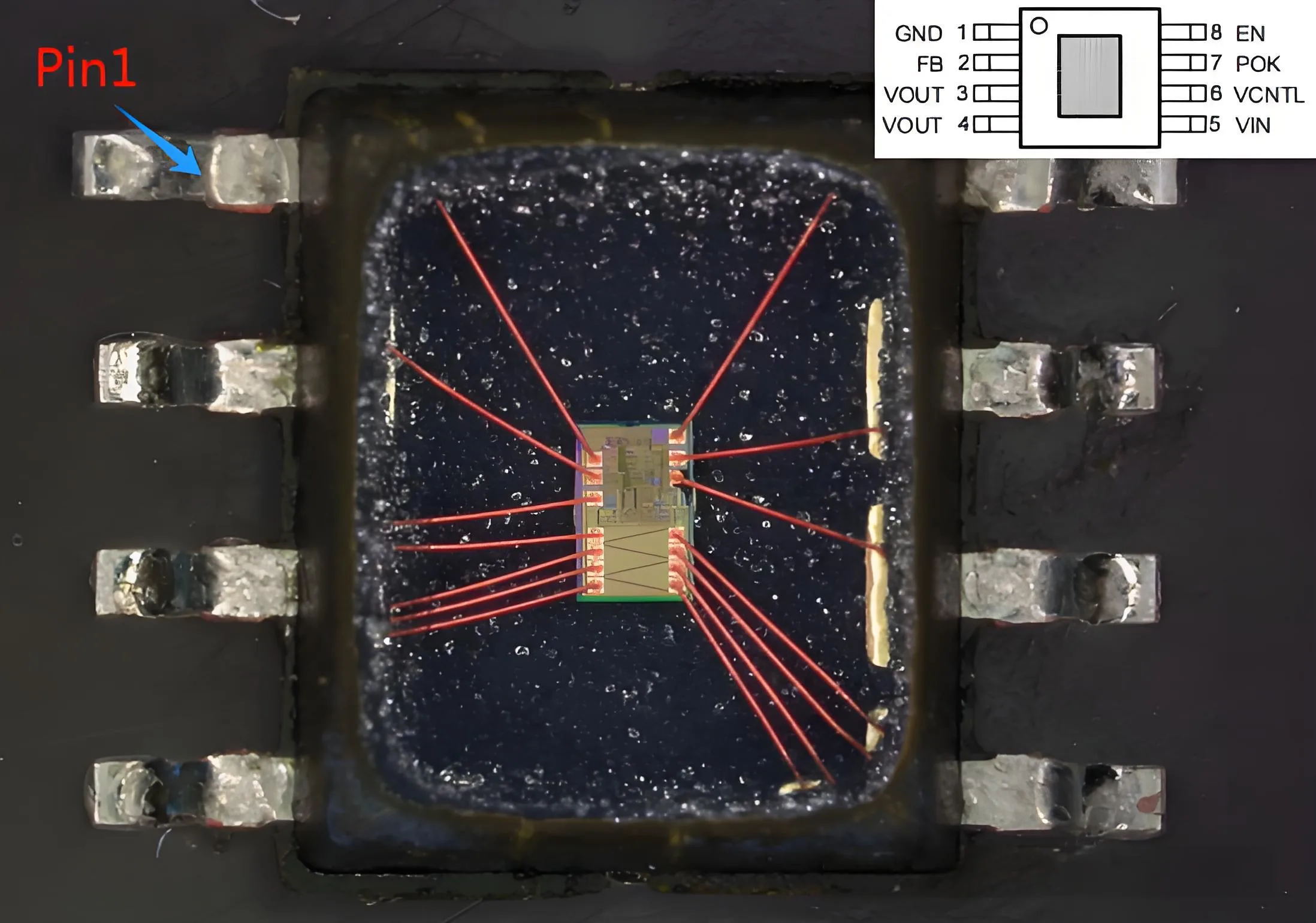

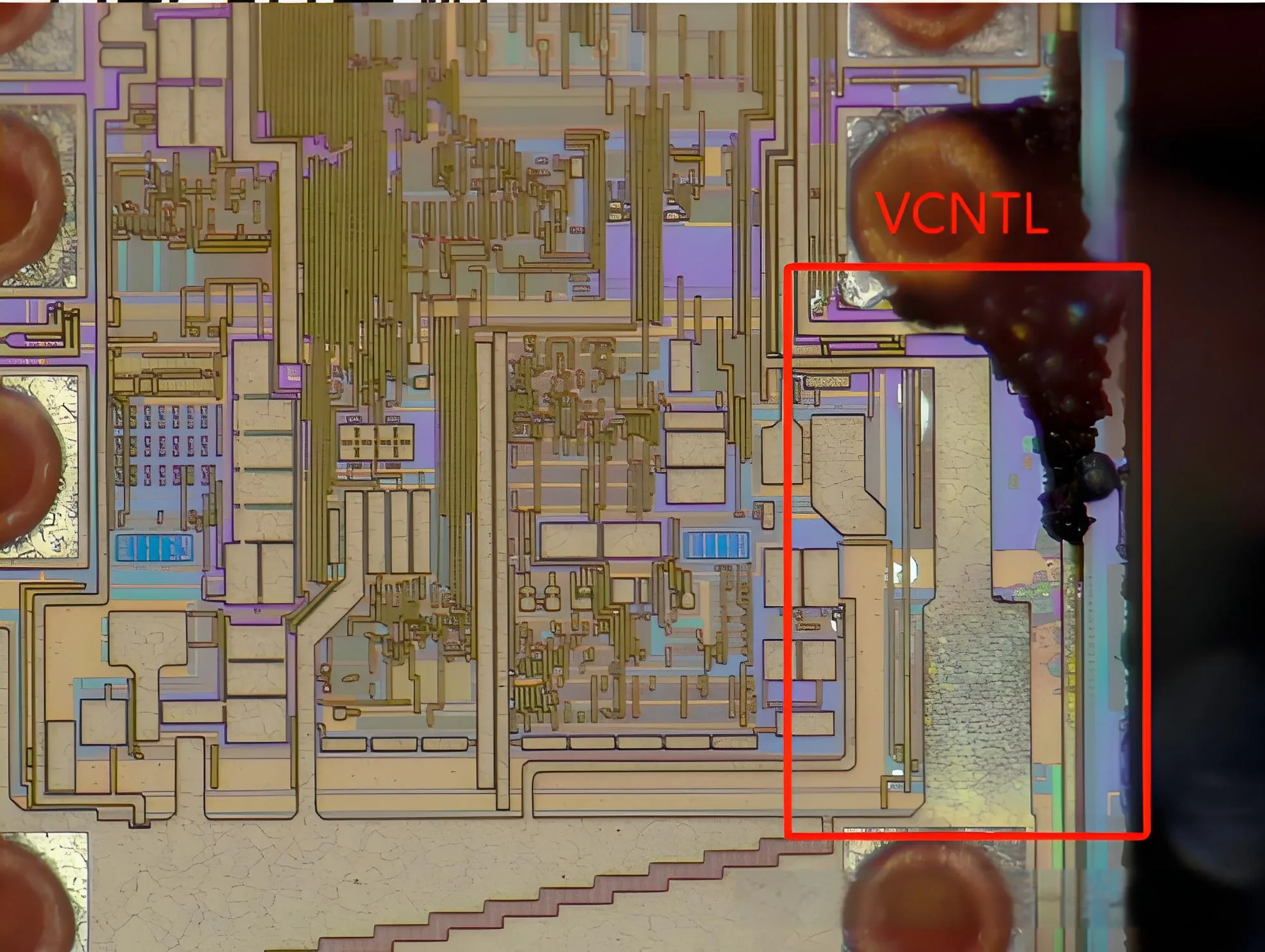

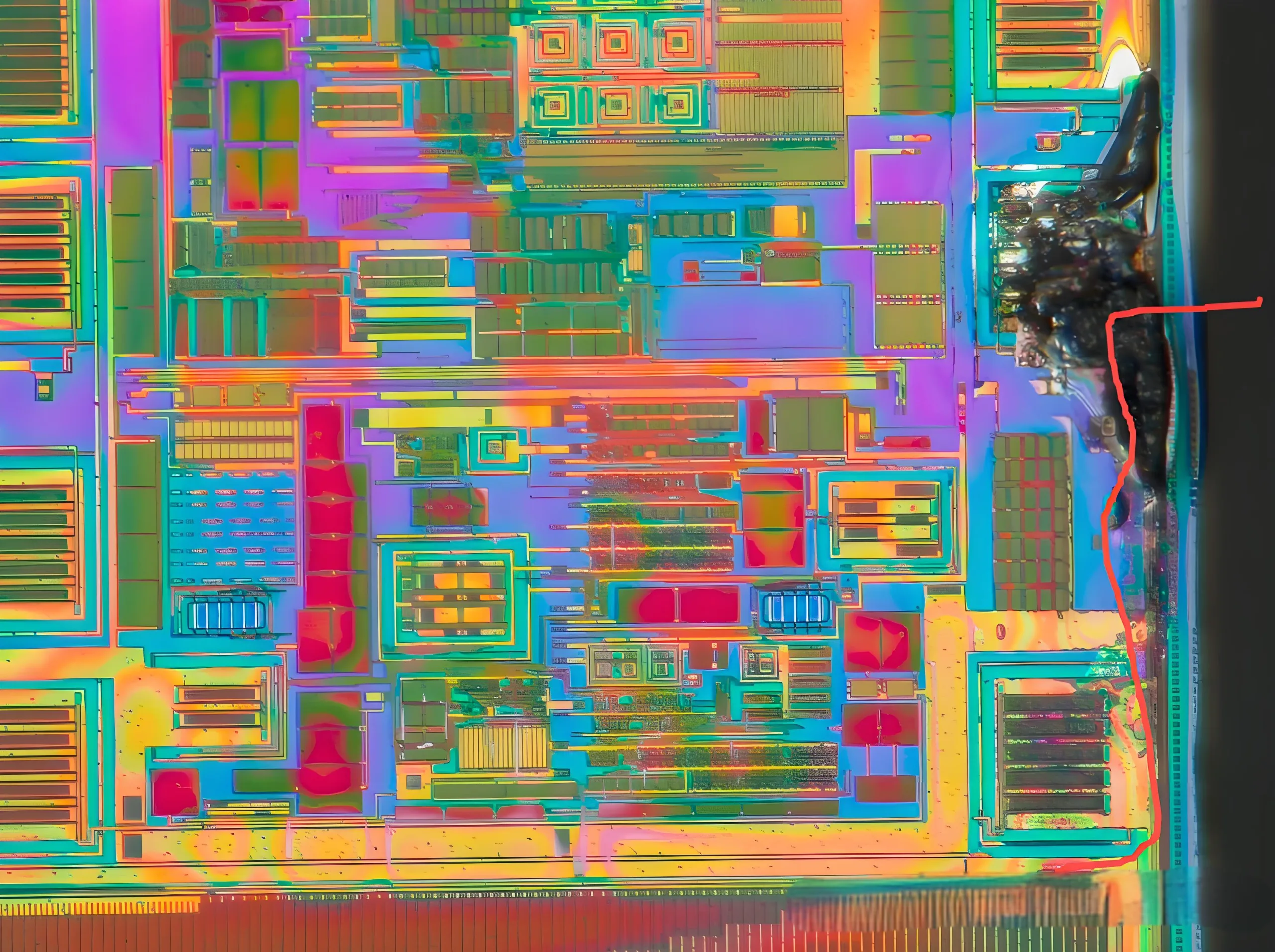

En ouvrant la couverture, Il a été constaté que l'épuisement professionnel de la puce était le plus sévère à la broche VCNTL plutôt que VIN.

L'EOS de la puce a été brûlé

L'EOS de la puce a été brûlé

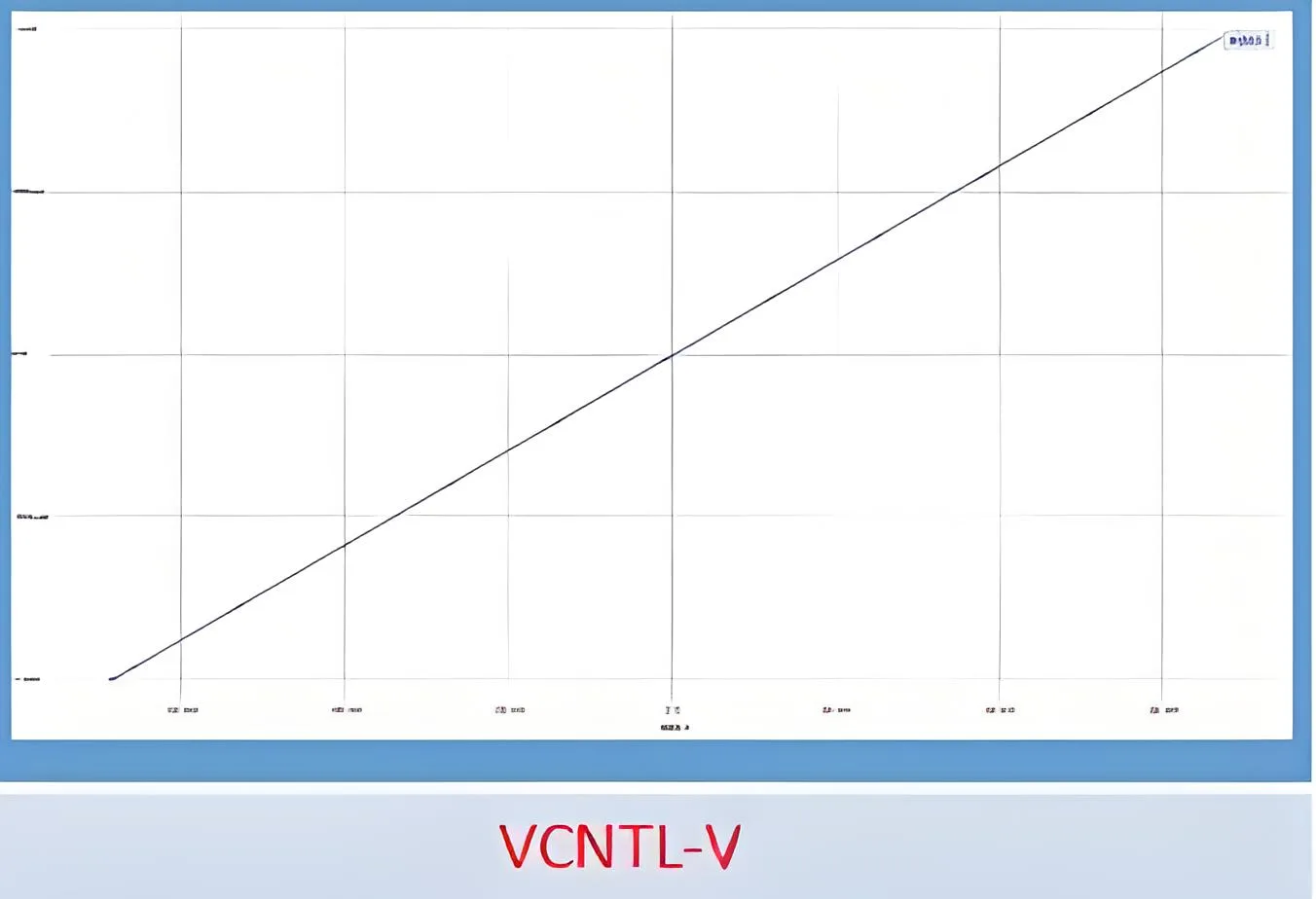

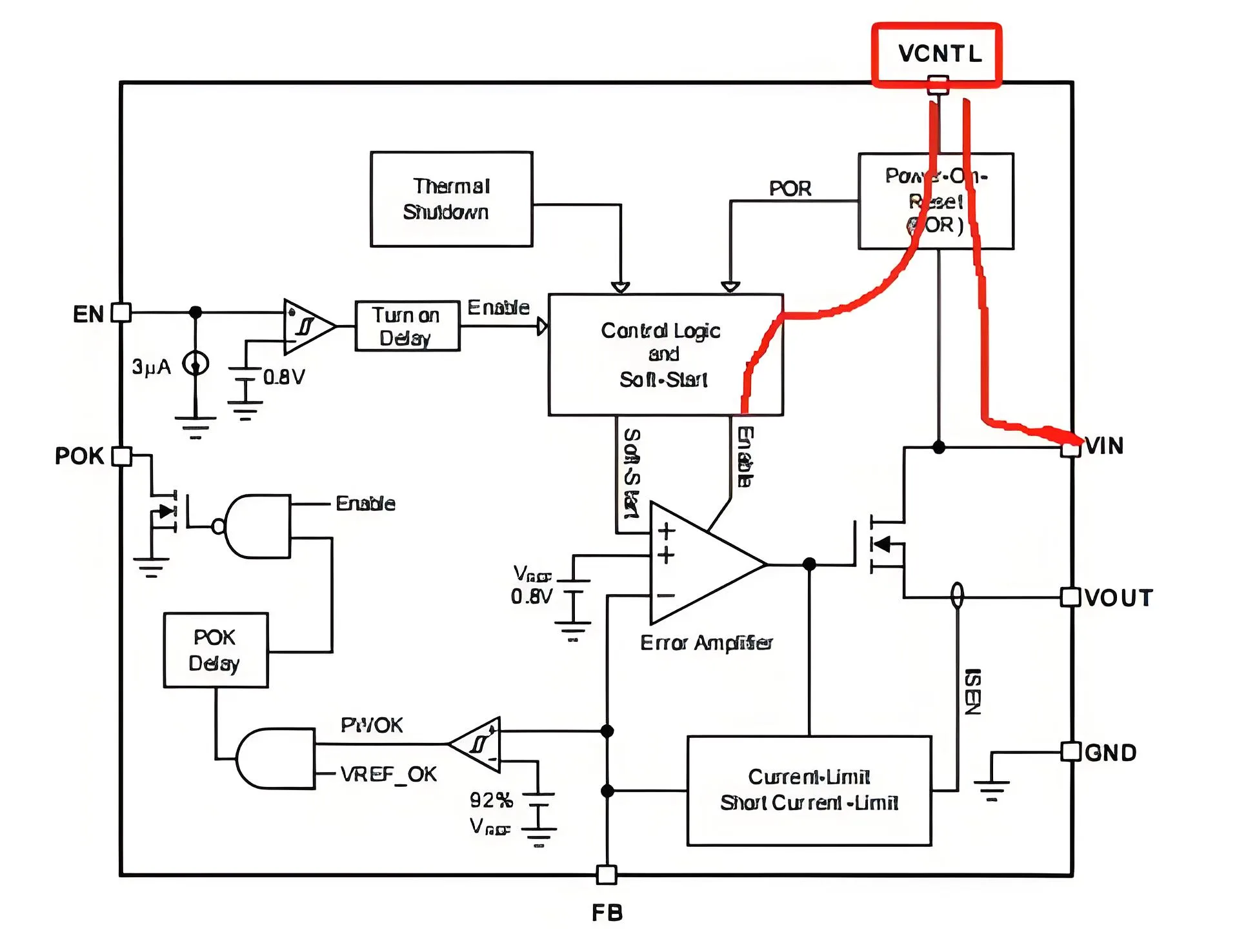

3) Analyse des causes profondes: On soupçonne que la contrainte de surtension introduite par VCNTL a provoqué la défaillance de la puce. La broche VCNTL est définie comme une broche d'entrée, ce qui pourrait potentiellement ressentir un stress sur tension sur tension.

VCNTL introduit une contrainte électrique excessive conduisant à une défaillance

Une analyse plus approfondie a révélé que la morphologie du métal le long du lien VCNTL-Vin semblait fondu, et la mesure de l'IV entre VCNTL et VIN a montré un court-circuit. Donc, La puce a échoué en raison de la contrainte de surtension introduite par VCNTL. L'analyse du schéma de bloc logique de la puce correspondait au phénomène de défaillance avec sa fonction logique.

Diagramme logique de puce

La suppression de la couche supérieure de métal a précisé que la défaillance de la puce était en effet causée par la contrainte de surcoltage introduite par VCNTL.

VCNTL introduit une contrainte électrique excessive conduisant à une défaillance.

VCNTL introduit une contrainte électrique excessive conduisant à une défaillance.

4) Confirmation du niveau du conseil: Après analyse, Il a été confirmé que des dommages à d'autres dispositifs périphériques de la carte ont provoqué la contrainte de tension sur la broche VCNTL dépassant sa valeur de spécification. Ainsi, Cette puce était un “victime.”

L'EOS est le phénomène le plus courant rencontré dans l'analyse des échecs. L'identification de la cause profonde par le biais de symptômes d'échec de l'EOS est difficile et nécessite que les analystes aient une réflexion logique claire et des connaissances approfondies.

LOGO UGPCB

LOGO UGPCB